Other Parts Discussed in Thread: PCA9306, LSF0102, , LSF0002

Tool/software:

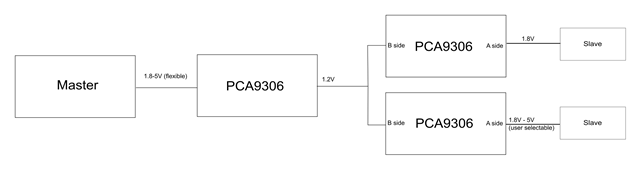

I have a case where I need an I2C star topology translator. One slave bus must be set to 1.8V. The other slave bus is user-selectable between 1.8V and 5V. The master bus voltage is flexible. (See diagram)

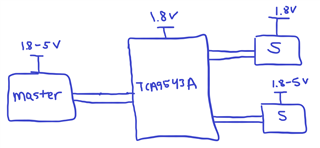

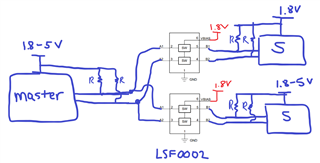

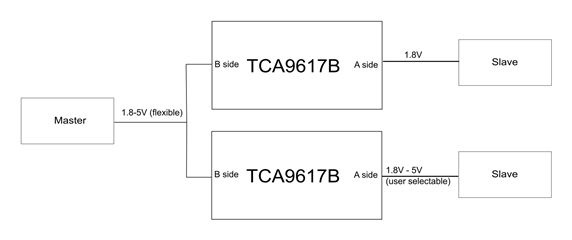

The TCA9167B almost works except the requirement that the A-side has to be on the common side of the star topology. If I use that topology, the B-side voltage doesn’t support down to a 1.8V bus. So I’m wondering, can I run a star topology with the B-side on the common bus? I realize that the one 9617 on the bus won’t see the low logic driven from the other 9617, but does the I2C bus still function properly? Is the concern that the inactive slaves could see erroneous clock/data that causes them to misbehave? Why can't the B side be used on the common bus other than the logic level drive/threshold limitation?

Another option is to run VccB at 2.2V with pull-ups to 1.8V. This should still meet the logic high threshold (ie 0.7 * 2.2V = 1.53V), but I’m concerned that it will be difficult to run at 1MHz given that the logic high is near the top end of the RC time constant.

If this topology doesn’t work, can anyone suggest an architecture that would? I need FM+ with one I2C bus at 1.8V and another I2C bus at a user-selectable voltage between 1.8V and 5V.

Thanks,

Ned