Other Parts Discussed in Thread: AM5716

Tool/software:

Hi TI Team,

How to set RX_CLK polarity reversal for DP83822 chip in MII mode?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi TI Team,

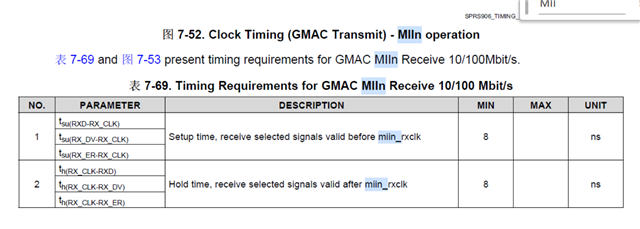

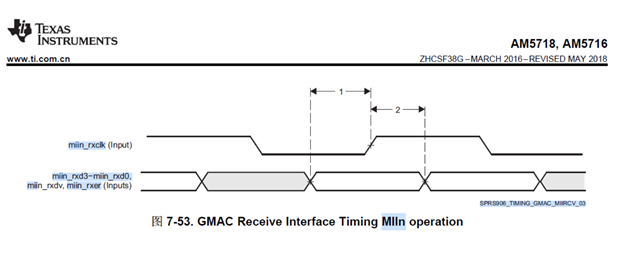

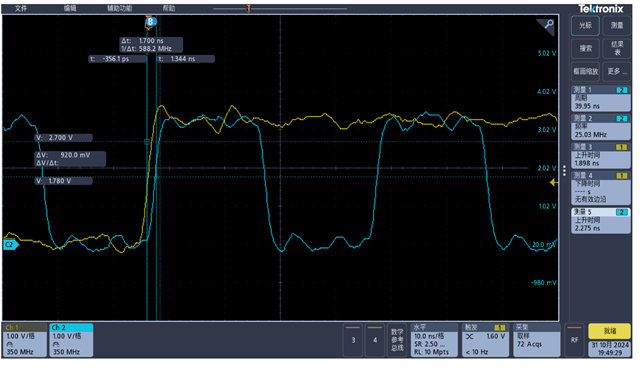

We actually have a issue of timing about RX_CLK in MII mode as shown below. The AM5716 specification requires a minimum setup time and hold time of 8ns,It is obvious that 1.7ns does not meet the specification. So how to set DP83822 to meet the specifications, RX_CLK polarity reversal or clock shift ?

Hi Jie,

Thank you for submitting your query. Before diving into the details, could you share what the root issue is? Is it packet loss or unable to transmit data? Do we have link?

Please share more context as to what the problem is and what led you to look at the MII signals.

Regards,

Alvaro

Hi Alvaro,

Thanks for your support.

The speed of RX direction is very low around 300KB/s (normal is around 2.2MB/s) through the FTP tool transferring files, The speed of TX direction is normal, The link has not been down.The failure rate is 10%,It is our root issue.That's why we're checking the MII RX signal.

Let me share with you our debugging action.

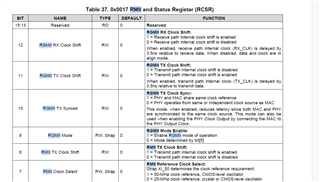

The RX transfer rate can be increased to about 2.2MB/s after seting the RCSR(0x0017) bit 12 from 0 to 1, waveform shows setup time is 4ns.

Therefore, we highly suspect that the low speed is caused by the setup time not meeting the specifications. 4ns still does not meet the AM5716 specification, how to set setup time> 8ns.

Hi Alvaro,

Sorry, I have to correct the information. We double checked the DP83822 Settings and found that it was working in RGMII mode not MII mode.

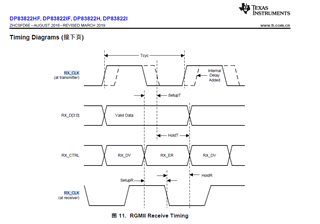

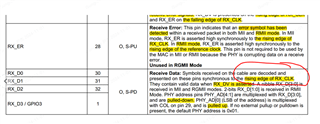

Data sampling reference clock falling edge if in RGMII mode,but pin function description section show the reference is clock rising edge. I'm confused,Could you give me some advice.

Hi Jie,

Thank you for adding more context to the issue and describing the debug steps taken.

The speed of RX direction is very low around 300KB/s (normal is around 2.2MB/s) through the FTP tool transferring files, The speed of TX direction is normal, The link has not been down.The failure rate is 10%,It is our root issue.That's why we're checking the MII RX signal.

I agree that the issue is likely within the MAC Interface.

We double checked the DP83822 Settings and found that it was working in RGMII mode not MII mode.

To confirm, when the DP83822 is configured for RGMII mode, everything works fine and there is no issue. The issue occurs only when we use MII?

What is the desired MAC interface? It is very important that both the MAC on the AM5716 and the DP83822 are configured in the same MAC interface (MII or RGMII in this case). For example, in MII mode, the PHY provides both TX_CLK & RX_CLK. In RGMII, the PHY only provides RX_CLK and the MAC will provide TX_CLK.

Regards,

Alvaro

Hi Alvaro,

Sorry to confuse you,The root issue occurs in the RGMII mode. It has been RGMII mode since the issue occurred,the desired MAC interface is RGMII.

Now let's discuss the issue based on the RGMII mode.

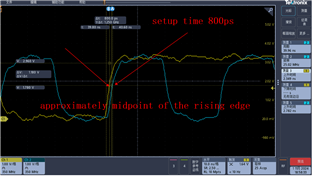

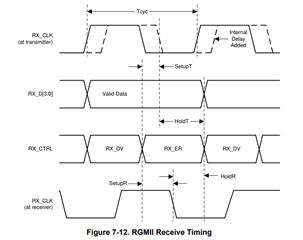

If refer to the RX_CLK clock rise edge, the waveform shows that the worst setup time is 900ps<1ns (RGMII spec), and the best can be 1.7ns>1ns.I suspect that's the problem,So setting RCSR register bit 12 from 0 to 1 can fixes the issue.

But I'm not sure if the data refers to the rising or falling edge of the RX_CLK.

Hi Jie,

Thank you for confirming. Does enabling the RGMII RX_CLK Shift (RCSR Reg 0x17[12]) solve your issue?

In RGMII, the data is sample on the rising edge of the clock for 10/100Mbps speeds. At 1000Mbps, the clock is sampled at both the rising and falling edge.

Regards,

Alvaro

Hi Alvaro,

Yes,Enabling the RGMII RX_CLK Shift (RCSR Reg 0x17[12]) can solve our issue.Do you think the root cause is that RGMII RX_CLK Shift is not enabled? RGMII RX_CLK Shift should be enabled or disabled?

Another question related to waveforms.

When we use an oscilloscope to measure the setup time, the cursor should be aligned at 50% of the amplitude or the midpoint of the rising edge, right? We don't find an introduction in Std 802-3,If you have relevant introduction documents, could you email to me.My E-mail address is: yinjie1@sungrowpower.com

Hi Jie,

Thanks again for confirming. Yes, RGMII RX_CLK Shift not being enabled is the root cause of this issue. Please keep it enabled. We want the clock to be slightly behind the data, so that when the rising edge of the clock comes, the data is sampled in the correct state.

In the scope capture you shared, the blue signal is RX_CLK and the yellow signal is RX_CTRL correct? RX_CTRL is supposed to trigger on the rising edge of RX_CLK, seems like it is doing exactly that! Regardless, if communication is working with RX_CLK shift enabled, I wouldn't worry about the setup and hold times anymore.

Regards,

Alvaro

Hi Alvaro,

I agree. I also think that's the root cause.

But I still have a few questions about the specifications.

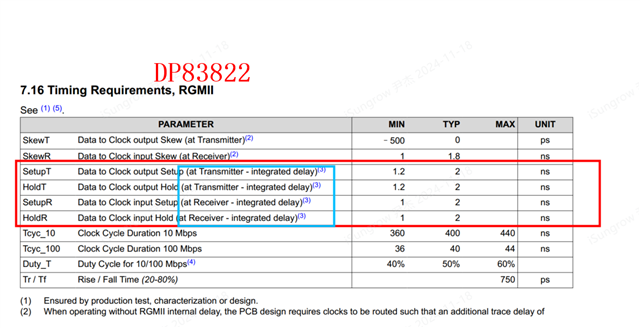

One question for the DP83822 specification is "integrated delay" as shown in the blue box below.Does it refer to PHY internal delay or MAC internal delay?

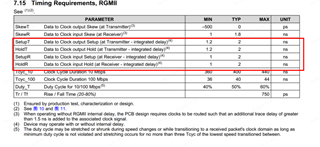

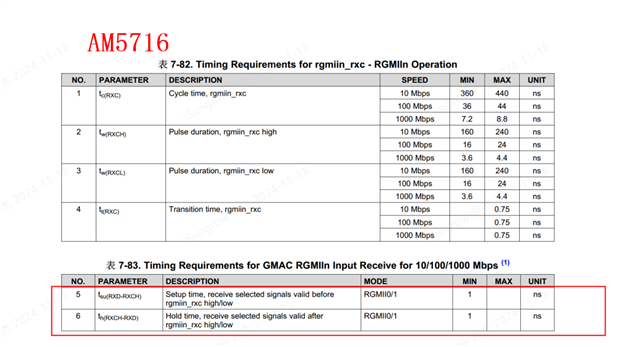

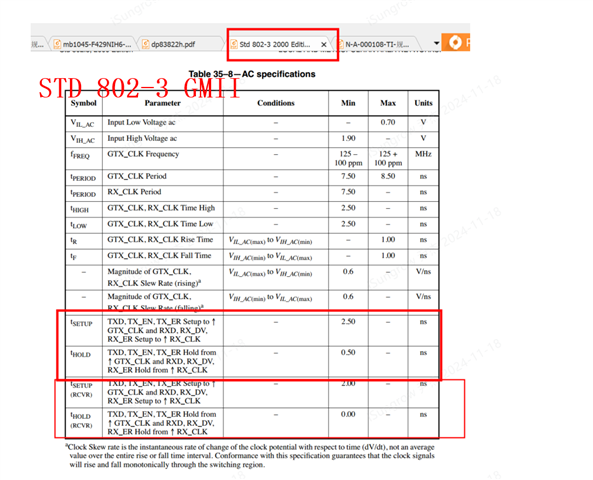

Another question is the difference between the AM5716 specification and the 802-3 standard.The 802-3 standard shows that the setup/hold time are 2ns/0ns, and the rise/fall time is 1ns/1ns. However, the AM5716 specification shows that the setup/hold time are 1ns/1ns, and the rise/fall time is 0.75ns/0.75ns.These differences confuse me. Could you give some comments.

Note: The RGMII specification is not found in the 802-3 standard, I just refer to the GMII specification in the 802-3 standard.

Hi Jie,

I'll gladly continue to support, could you confirm if the current issue is resolved, i.e. are you able to send data successfully now that the RGMII CLK Delay is set?

One question for the DP83822 specification is "integrated delay" as shown in the blue box below.Does it refer to PHY internal delay or MAC internal delay?

This could refer to either, both the DP83822 or the MAC can introduce delay. I have seen that several TI processors have a default delay on TX_CLK that cannot be disabled, so the TX_CLK delay on the DP83822 should be disabled (Reg 0x17[11] = '0') and the RX_CLK delay should be enabled (Reg 0x17[12] = '1').

Spec comparison can often cause confusion and the GMII spec is not apples-to-apples. Please find the RGMII spec below. The data to clock delay is referred to as Tskew in the standard.

Regards,

Alvaro

Hi Alvaro,

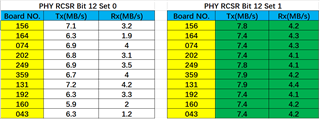

Yes,The current issue is resolved.Below are the test results of 10pcs board.

First, The Rx rate can reach 4.2MB/s,That's OK;

Second, Please pay attention to the Tx speed.The rate of Tx also increases a bit (about 7MB/s->8MB/s) when RCSR Reg 0x17[12] is set to 1.

It's so confusing that RCSR Reg 0x17[12] affects Tx rate .Could you give some comments.