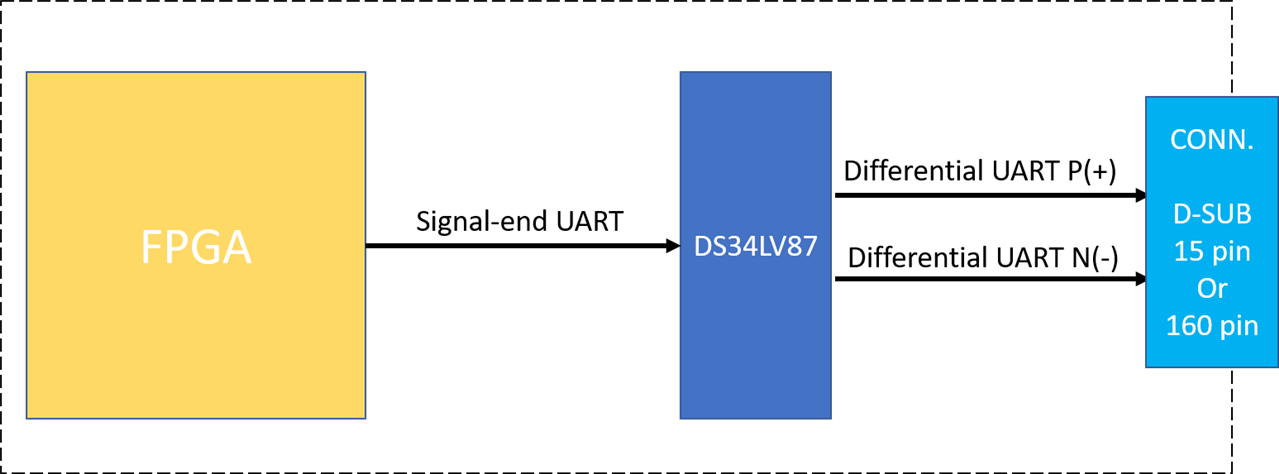

Tool/software:

Hi sir,

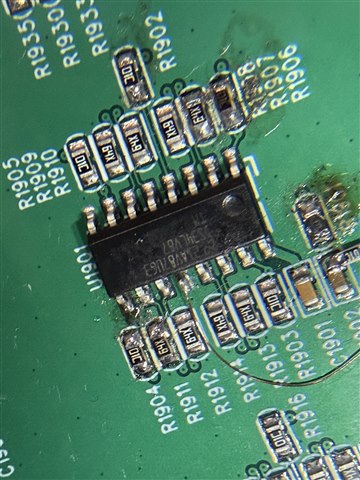

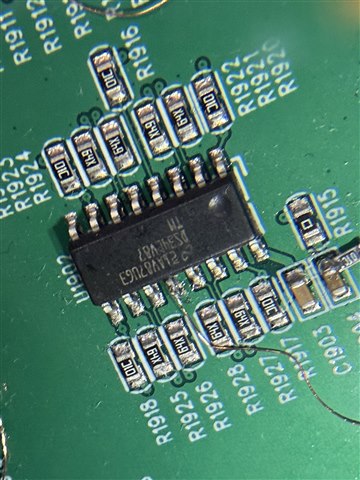

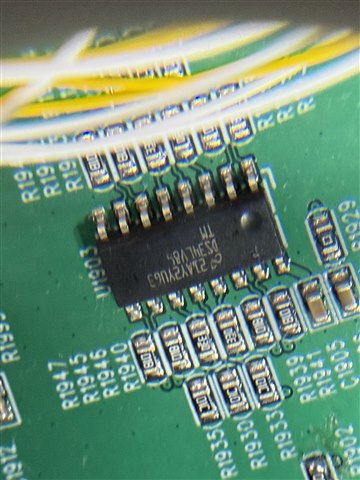

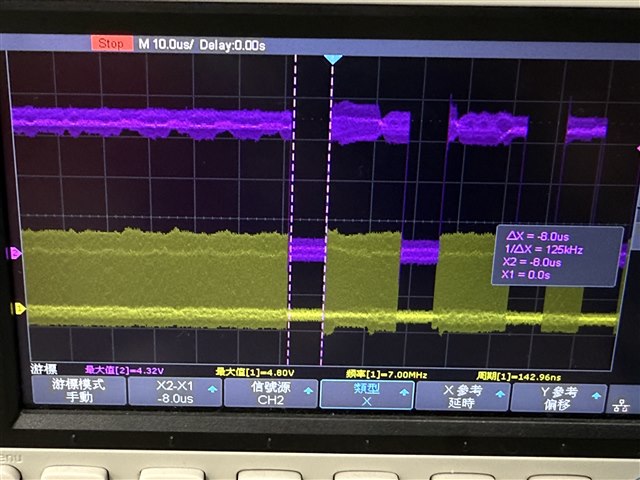

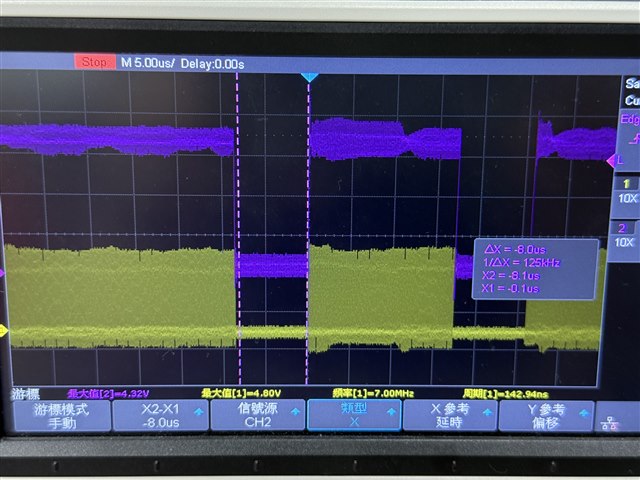

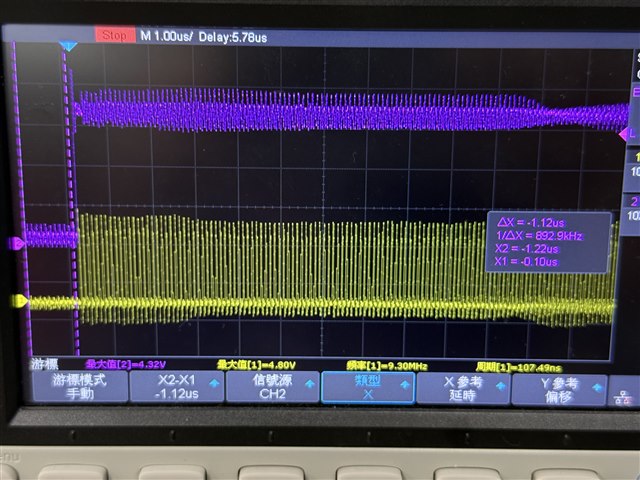

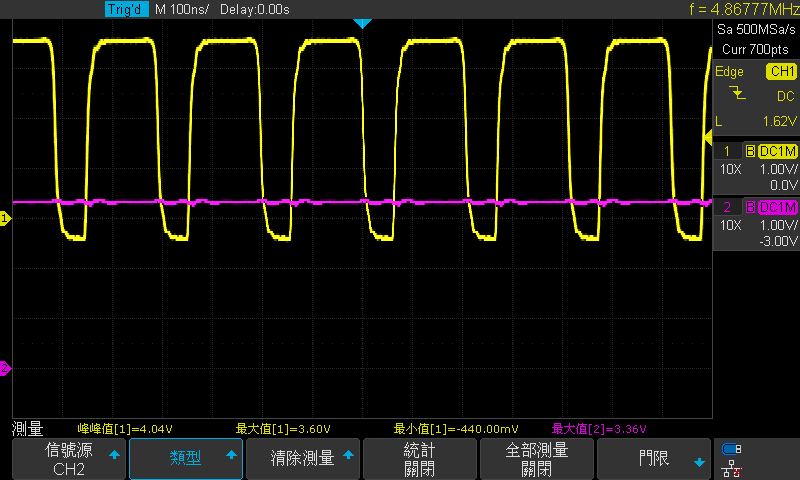

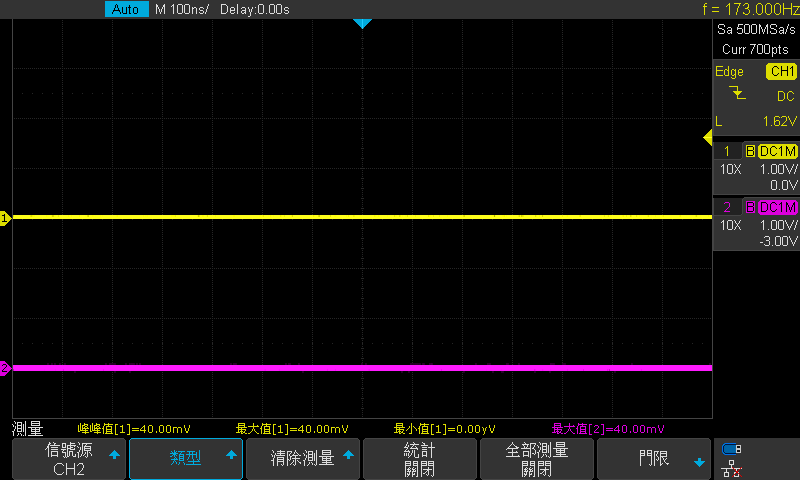

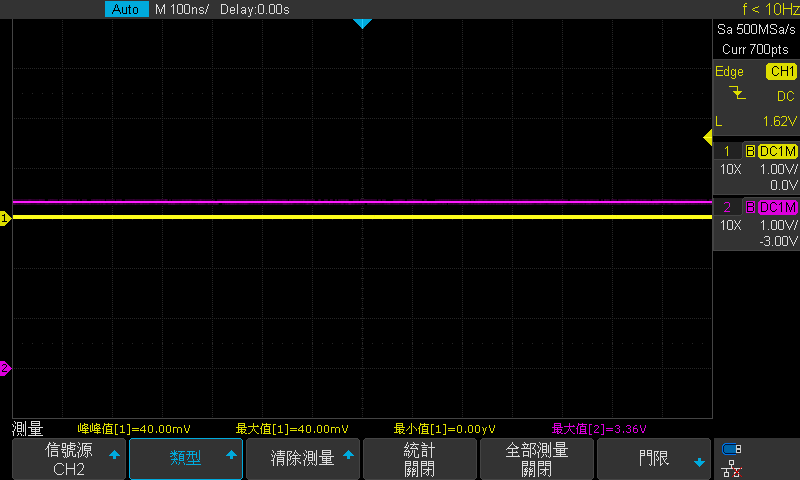

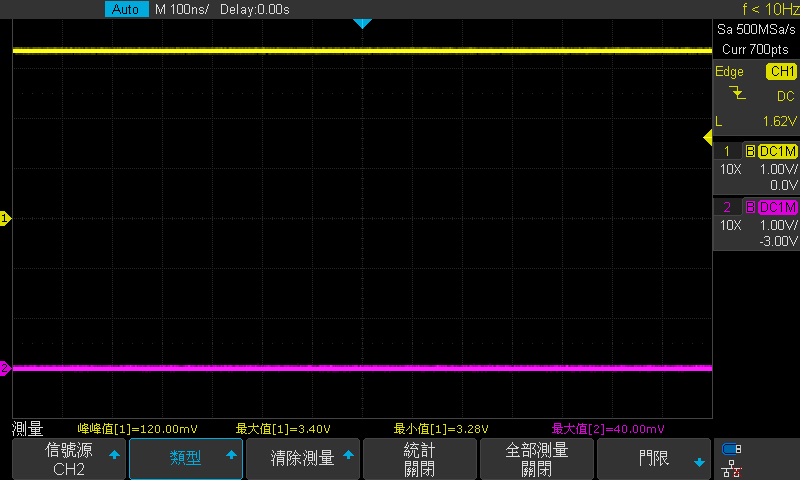

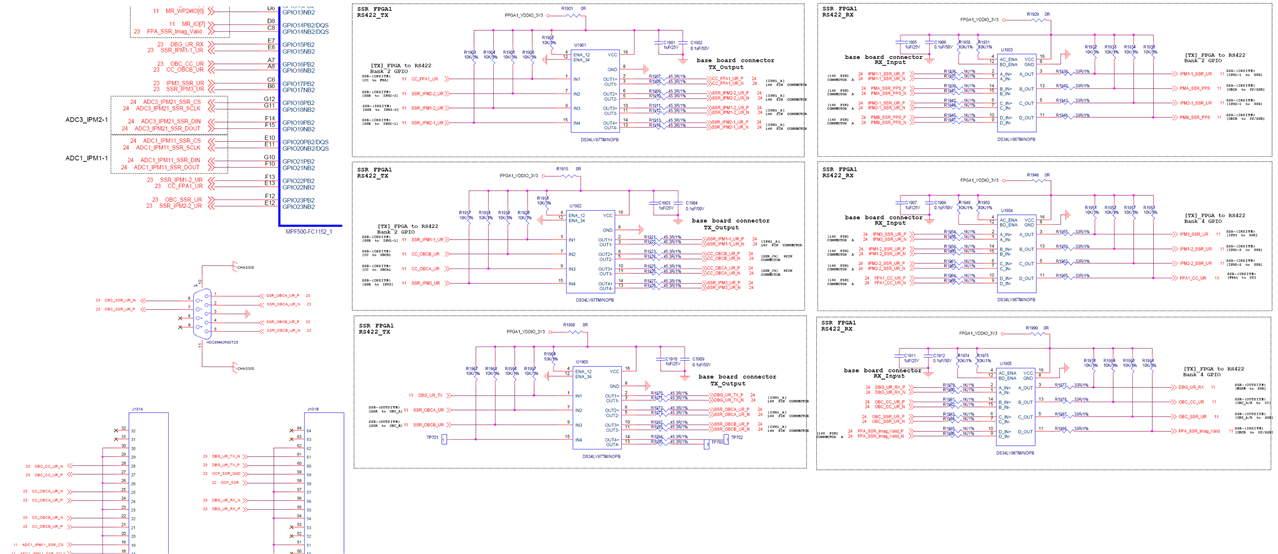

Our system uses three DS34LV87T chips to convert the UART signal from single-ended to differential. Currently, we are encountering a problem where the output P exhibits the waveform shown in the image below when there is no input signal connected.(only pull-up)

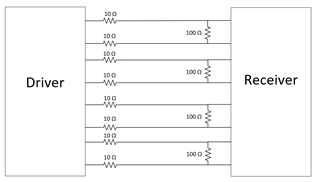

All three ICs are experiencing the same issue. We have attempted to add termination resistors 100 Ohm to the output to prevent it from being left floating, but this has not resolved the issue.

The output N does not produce any waveform.

However, strangely, this state still allows for normal transmission of the UART signal.