Part Number: DS250DF810

Tool/software:

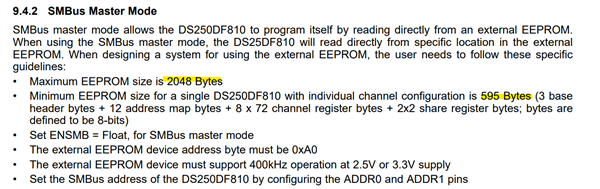

1: The chip load from extern eeprom,how to deal with the pin en_smb(E3) and read_en_n(F13) ?both are pull down?

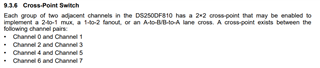

2: how is the crosspoint of DS250DF810 ,please supply a pciture

3: the apply is 100G over 4 lane in zqsfp+,please supply eeporm file.

4: the designe use two the chips,the pin cal_clk_in use the crystal separately, the pin cal_clk_out (E15) is noconnection,is this ok?

5:what is the price and how to buy it in beijing of china