Other Parts Discussed in Thread: TCA9511A

Tool/software:

Hello support team,

As we've discussed before, Vref2's voltage stability has a lot to do with the behavior of PCA9306.

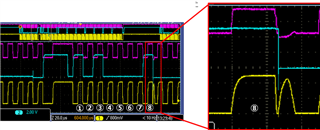

When there is the noise coming from the system resulting the Vref2 dropping below recommendation (2.1V), the chip will work abnormally.

However, adding a decoupling cap at Vref2 to avoid the noise would be the great solution to resolve this problem.

My customer is already doing the next generation project adding the decoupling cap, however, they still need to resolve the problem that those end equipment being already released.

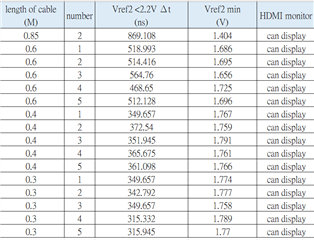

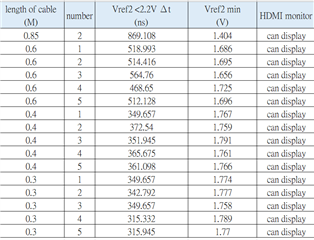

They've ended coming up with the shorter cable to reduce the noise, please see the chart of the experiment below:

What we want to ask is that, is there the timing requirement that between what timing could the chip still works correctly?

I have two assumptions here:

1. more than about a period, Ex: 5us. Since the data we got are all smaller than 1us, and we can convince the customer that this is the short-term solution.

2. based on your experience, the data above would be able to support, but we do not have the numerical data at hand.

Could you please help to give some suggestion?

Thanks.

Dave