Part Number: TRS3221E

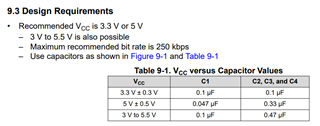

Tool/software:

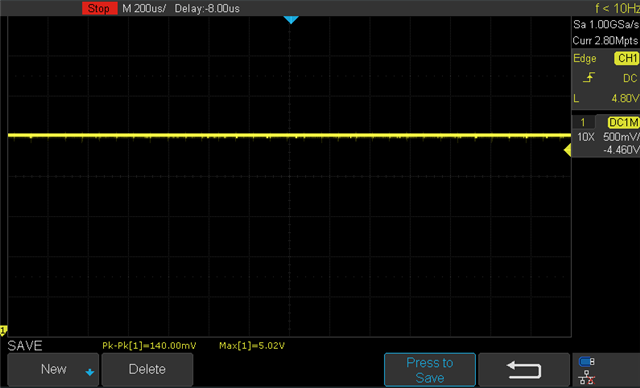

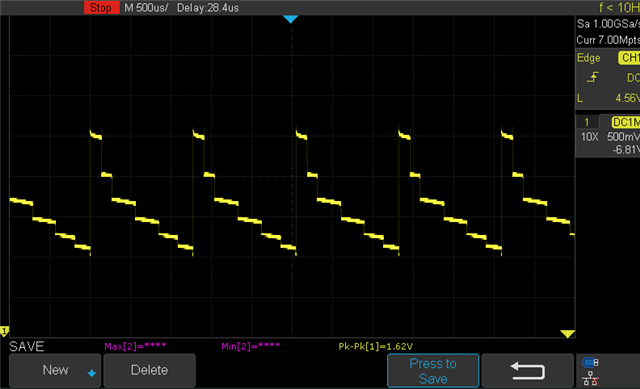

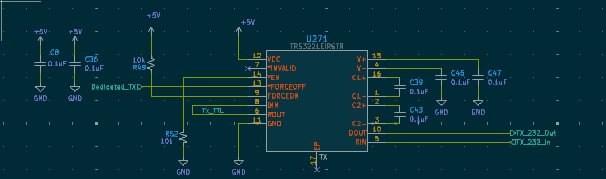

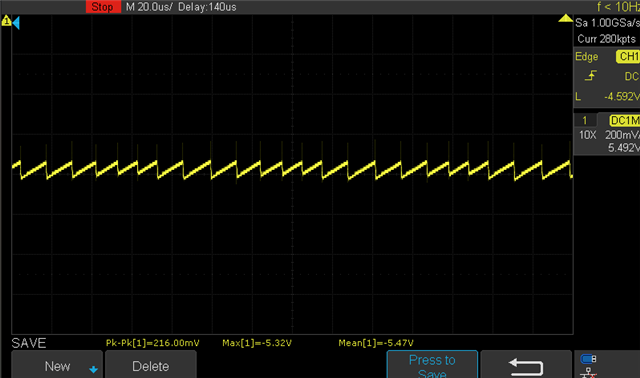

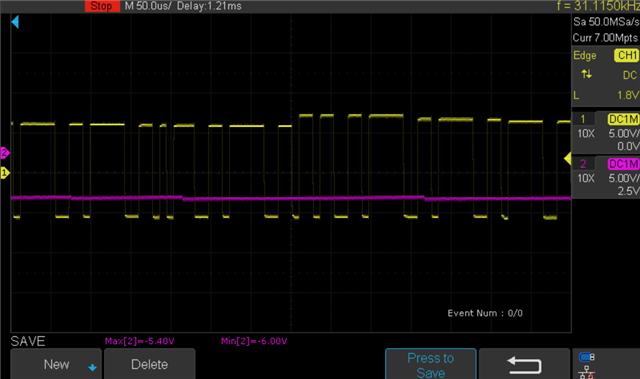

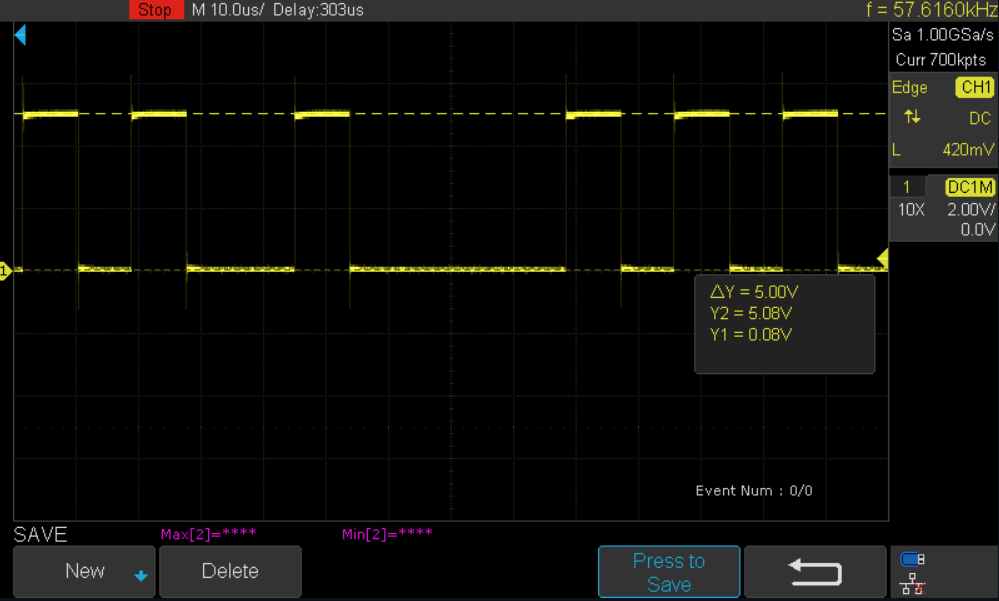

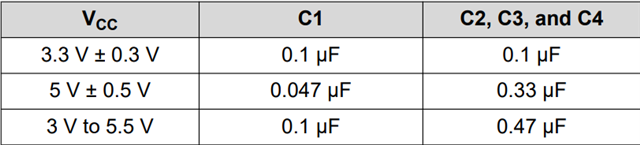

I am using the TRS3221EIRGTR RS-232 transceiver in my design and am noticing significant ripple noise on the V+ rail. The supply voltage is 5V, and I have placed a 0.2µF bypass capacitor between Vcc and ground. Initially, I used 0.1µF capacitors for the charge pump, and with this setup, I observed a ripple voltage of approximately 1.5V on the V+ rail. The capacitors are placed on the bottom of the PCB, right next to the pins of the transceiver, so I do not believe it is a layout issue. When observing an RS-232 signal at the DOUT pin with a load connected, the waveform shows a sawtooth pattern when the signal is high.

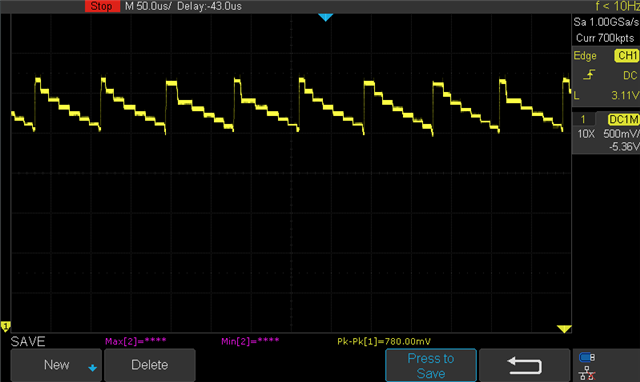

I reviewed the charge pump functionality in the application note, How the RS-232 transceiver’s regulated charge-pump circuitry works, and based on Equation 2 from the document, I attempted to reduce the ripple by adjusting the capacitor values. I changed the capacitor values C1 = 0.1µF and C2, C3, C4 = 0.4µF, which reduced the ripple to approximately 500mV. I also tried increasing the values to C1 = 0.1µF and C2, C3, C4 = 1µF, as suggested by the waveforms in the document, but the ripple voltage increased to approximately 650mV.

Are there any additional recommendations or techniques for further reducing the ripple on the V+ rail? Any insights would be greatly appreciated.