Part Number: TCA9416

Other Parts Discussed in Thread: SN74AXC4T245

Tool/software:

Hello,

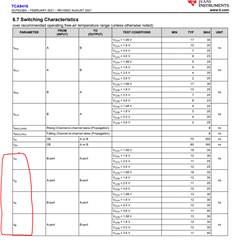

For SCL and SDA pins, does TCA9416 also have any maximum rise/fall time (tr/tf) spec like CMOS based level shifter as SN74AXC4T245?

Best regards,

Best regards,

K.Hirano