Other Parts Discussed in Thread: ESD2CAN24, CSD, CSD17483F4, CSD87502Q2

Tool/software:

Hi Team,

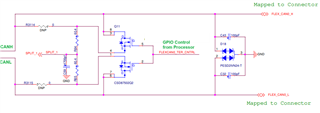

My application includes a CAN interface, which requires GPIO control for enabling and disabling the 120ohm CAN termination.

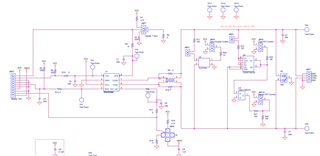

Referred to the TI Implementation shared below for this

can selectable termination.opj

Taking this as a reference, implemented the CAN termination control using GPIO as shown below

Could you please review this implementation and share your feedback?