Part Number: DP83848C

Tool/software:

Dear Sirs ,

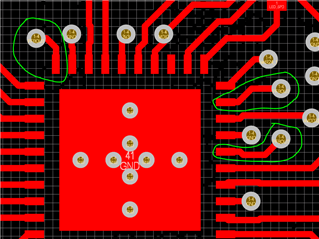

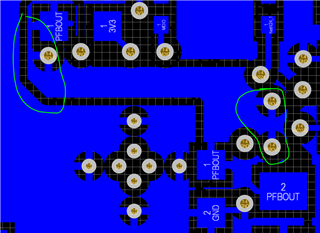

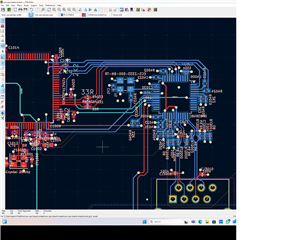

I am working on a layout with DP83848C and I am wondering if the PFBOUT 23 can be connected with a wire under the IC with pin 18 and 37 .

I have a bit a space constraint design and if I can rout them under the ic that would help