Part Number: DS90UB928Q-Q1

Tool/software:

Hello

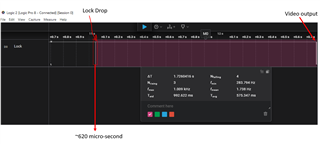

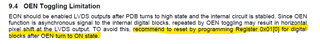

Could you help us to know the maximum time expected to be consumed by below reset digital blocks 0 ?

Also what is the impact for the chronogramme shown in the "Figure 6. FPD-Link Outputs Enable Delay" ?