Tool/software:

Hello:

We had some questions about an issue we are having with a system using the THVD1420 that we would be helpful to receive guidance for.

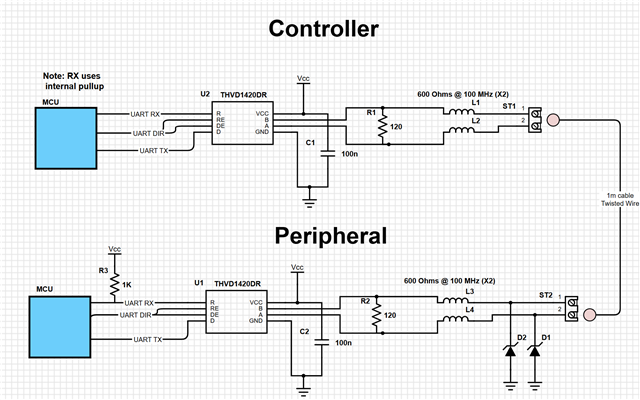

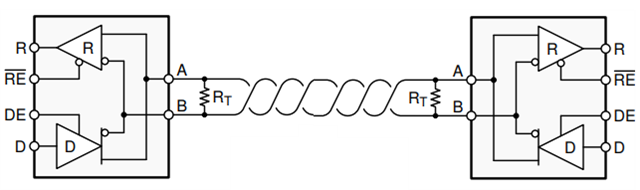

We have a device with two PCBs communicating via RS485 using the THVD1420. There is only two nodes in the interface - a controller and a peripheral, connected with a cable of around 1 meter. We use the same schematic as the one from section 8.2.2 of the datasheet.

Our system looks like this:

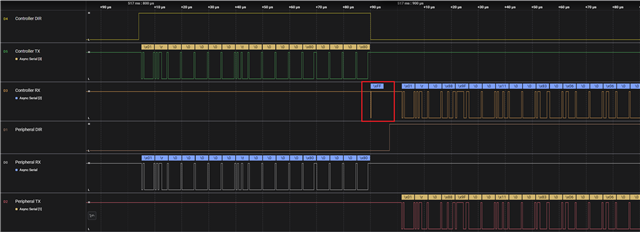

When communicating, the controller queries the peripheral with a message, and the peripheral replies with a response. The communication is always starter by the controller. When the controller sends data, it then starts to listen immediately on the line.

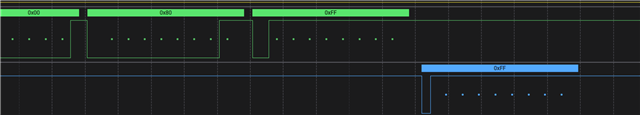

The issue we are having is that when the controller changes its direction pin from sending to receiving, the line is now idle, and there is a small glitch that makes the controller think it received a byte when it really did not. This small idle time is seen as a start bit by the UART peripheral of the MCU. This happens 90% of the time, which makes it difficult to just throw away the first bit received.

The write and read are controlled via DMA so it is hard to add a delay before reading (the DMA of this MCU is such that a TX+RX action chain can be defined as a single work unit).

My question is, what can we do to mitigate this issue? I was under the impression that the THVD1420 has fail safe resistors that should help with idle bus issues. Could it be that we need stronger resistors? Other than this issue, our communication at 2MBPS is very reliable, so I am doubting it could be an impedance mismatch between the cable and terminating resistor. But I could be wrong!

Below is a capture of the communications. I circled in red the glitch that happens when the controller changes from sending to receiving.

Any help on this is greatly appreciated!

Thank you,

-Eduardo Garcia