Other Parts Discussed in Thread: DS90UB948-Q1

Tool/software:

Hi,

We've recently had some issues with the DS90UB949-Q1 serializer chip and clock stretching.

For our hardware setup we have a main board with a STM32 (master), DS90UB949-Q1 and a PoE PSE on the I2C bus, and on our display side board we have the DS90UB948-Q1 and a couple of ADCs.

I have a couple of questions:

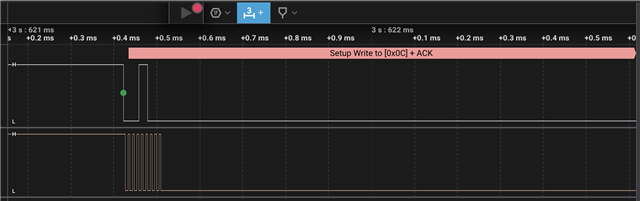

- Why would the DS90UB949-Q1 clock stretching we we're trying to write registers within itself? In AN-2173 it mentions that local operations do not need clock stretching

0x0C is the address of DS90UB949-Q1 - We are using DS90UB948-Q1 on the deserializer which is connected to the remote I2C and has a couple of ADCs that I've confirmed do not clock stretching. In what situation would the serializer need to clock stretch if the peripherals do not clock stretch? Would it be because packet loss?