Part Number: TIC10024-Q1

Tool/software:

Hello Support team,

I'm looking for the start-up timing of the MSDI TIC10024-Q1.

Can you provide us numbers for the following start-up scenarios:

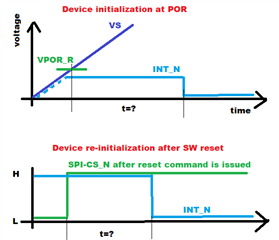

* Time from power-up (VS>=VPOR_R) until the device is initialized by default (resonator startup, self check, initialization).

* Time for re-initialization after a HW-reset or SW-reset

Best regards,

Andreas