Tool/software:

Hi team,

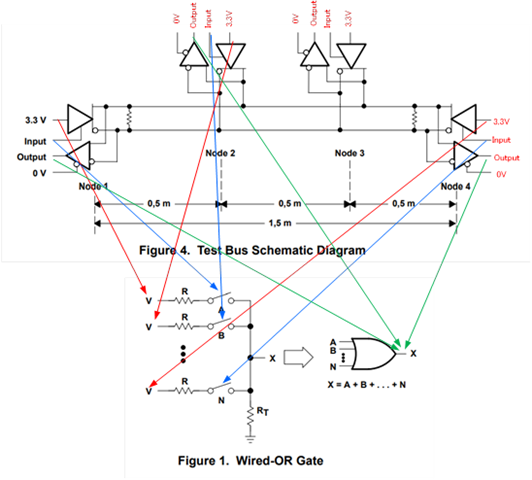

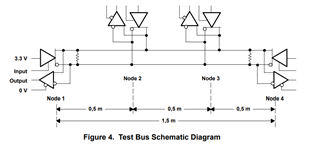

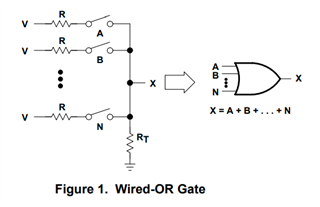

There are questions about the wired-of sinaling described in the app note, that is Wired-Logic Signaling With M-LVDS.

1. In the figure 4, is it no problem to make input pins of multiple devices High at the same time? Can this lead to device destruction?

2. Input pins in figure 4 can be equivalent to switches A~N in figure 1. Is this understanding correct?

Regards,

Noriyuki Takahashi