Other Parts Discussed in Thread: DP83869

Tool/software:

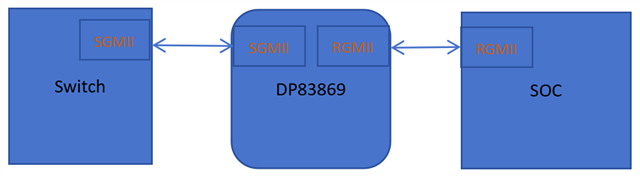

(1) I use dp83869 as a RGMII to SGMII Bridge to connect SOC and switch.

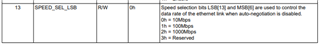

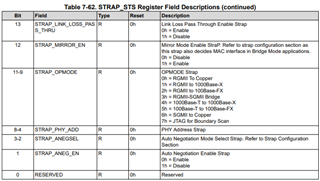

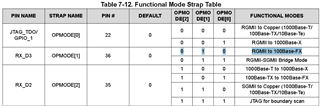

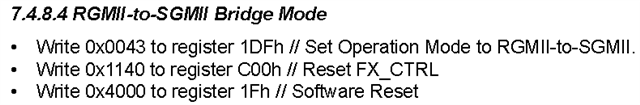

(2) I configured the following registers to make dp83869 work in bridge mode:

(3) After the configuration, when I power on the system, I found the switch SGMII and DP83869 SGMII can not link up each other.

Can you help to analyze the reason?

Thanks.