Other Parts Discussed in Thread: DS90UB949-Q1EVM, ALP, USB2ANY

Tool/software:

Hello,

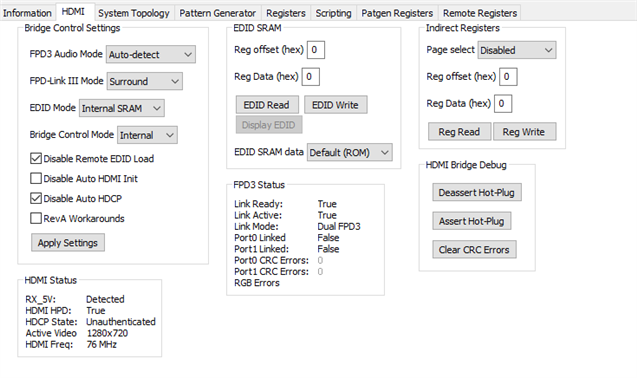

I'm using a screen display which incorporates a DS90UB948 deser. It is connected to a DS90UB949-Q1EVM and a successful FPD-LINK is established then using ALP software but there is no connection between deserialiser ?

Deser. I2C Address = 0x58

Serializer board all default settings done.

please guide the all necessary step to estabilish the connection between deser.

also share all required script and needfull settings in ALP software and serializer board.

Regards,

Abhishek Sonar

Tata Motors