Other Parts Discussed in Thread: TPD1E10B06-Q1, AM2732

Tool/software:

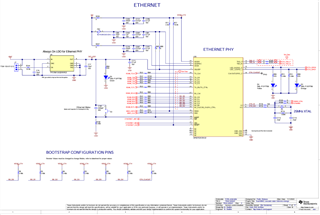

你好,我们使用TIDA020047开发板,需要使用83TC812芯片进行网络数据传输,但是我们配置了该芯片的寄存器后,却无法得到其输出的RGMII接口数据,通过示波器看了没有波形,不知道是否寄存器配置不正确,请帮我们核对一下:

REGADDR| DATA

0h | 0x2100| 1h | 0x0065| 2h | 0x2000| 3h | 0xA271| 10h | 0x2005| 11h | 0x010B| 12h | 0xE400| 13h | 0x0000| 15h | 0x0002| 16h | 0x0100| 18h | 0x5200| 19h | 0x0C0A| 1Bh | 0x0000| 1Eh | 0x0000| 1Fh | 0x0000| 41h | 0x88F7| 133h | 0x75EF| 17Fh | 0x4028| 180h | 0x0000| 181h | 0x0000| 182h | 0x0000| 183h | 0x0000| 184h | 0x0203| 185h | 0x000A| 187h | 0x0100| 188h | 0x0080| 189h | 0x0040| 18Ah | 0x0040| 18Bh | 0x1C0B| 18Ch | 0x0000| 18Eh | 0x8004| 300h | 0x2710| 301h | 0x1703| 302h | 0x0045| 303h | 0x0419| 304h | 0x0030| 305h | 0x0004| 306h | 0x000A| 310h | 0x0000| 430h | 0x0770| 444h | 0x0000| 450h | 0x2610| 451h | 0x0008| 452h | 0x0000| 453h | 0x0001| 456h | 0x0000| 457h | 0xE581| 458h | 0x0001| 45Dh | 0x028C| 45Fh | 0x000C| 485h | 0x1078| 486h | 0x0A05| 489h | 0x0001| 496h | 0x044C| 497h | 0x01C0| 4A0h | 0x1000| 553h | 0x0000| 560h | 0x07E4| 561h | 0x0801| 562h | 0x8028| 600h | 0x0038| 601h | 0x0000| 602h | 0x0000| 603h | 0x0000| 608h | 0x007B| 609h | 0x0000| 60Ah | 0x0200| 60Bh | 0x0005| 60Ch | 0x0024| 60Dh | 0x0000| 618h | 0x0000| 619h | 0x0574| 61Ah | 0x05DC| 61Bh | 0x007D| 61Ch | 0x0000| 61Dh | 0x0000| 61Eh | 0x0000| 620h | 0x0000| 622h | 0x0000| 623h | 0x0000| 624h | 0x5511| 625h | 0x0000| 626h | 0x0000| 627h | 0x0000| 628h | 0x0000| 629h | 0x0000| 62Ah | 0x0000| 639h | 0x0001| 63Ah | 0x0000| 63Bh | 0x0000| 63Ch | 0x0002| 63Dh | 0x0000| 63Eh | 0x0000| 648h | 0x0120| 649h | 0x0001| 64Ah | 0x0010| 871h | 0x00EE| 1000h | 0x0000| 1001h | 0x0004| 1007h | 0x003D| 100Bh | 0x0800| 1012h | 0x0001| 1834h | 0xC000| 1836h | 0x0000| 3000h | 0x0000| 3001h | 0x0004|