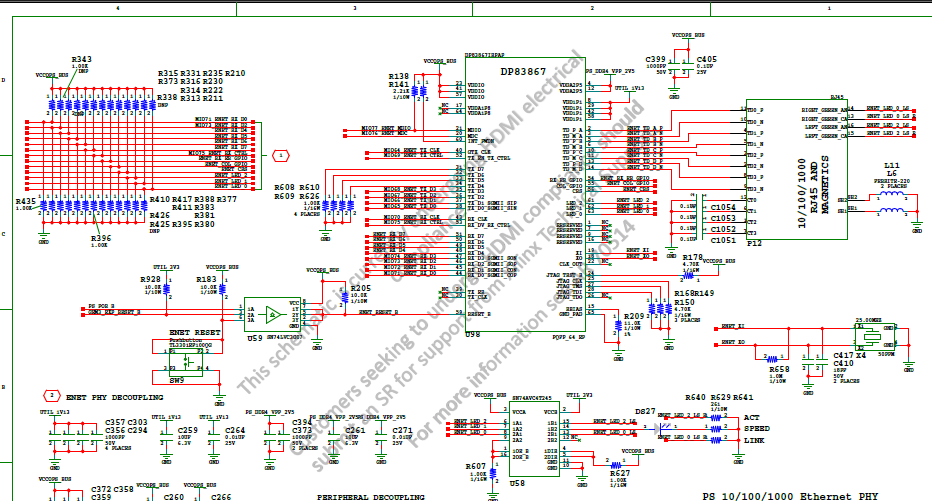

Part Number: DP83867IR

Tool/software:

Setup:

- Using DP83867 PHY in RGMII mode.

- Observing differences between a working board and a non-working board.

- Focus is on strap pins (e.g., RX_D0, RX_D2, RX_CTRL) and MDIO/MDC communication

Schematic:

Power-Up Observations:

- Working Board:

- RX_D0 is consistently low during power-up and reset.

- RX_D2 is consistently low during power-up, matching expected behavior.

- PHY communicates over MDIO/MDC, and MDIO/MDC toggling is observed.

- Non-Working Board:

- RX_D0 is high, even though it is pulled low in the schematic.

- RX_D2 is also low, matching the working board.

- MDIO/MDC do not toggle, and PHY is unresponsive to MPSOC commands.

Connection to PC PHY:

- Despite these issues, the PHY on the non-working board successfully establishes a 100 Mbps link with a PC.

- RX activity is observed via LEDs, indicating basic link functionality.

Request for Assistance:

- Does the power sequencing of VDDIO relative to VDDA and VDD1P1 directly affect strap pin behavior?

- Could slow ramping of VDDIO cause the PHY to incorrectly latch RX_D0 as high?

- Are there other possible causes for RX_D0 being high despite a pull-down resistor in the schematic?