Part Number: DP83825I

Tool/software:

Hi team,

DP83825I did not recognize TX properly when operated as slave mode.

However, when I enabled RMII_TX_Clock_Shift, it worked fine.

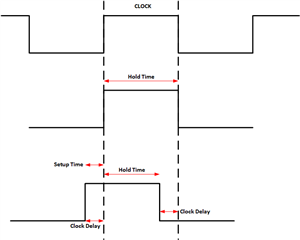

I assume this is due to the fact that there was no hold or setup time provided for the TX, correct?

I also did not know which time is clock shifted when this register is enabled at this time.

Can you please tell me where to look in the datasheet?

Best Regards,

Ryu.