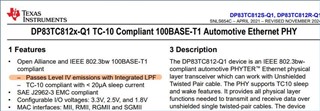

Part Number: DP83TC812S-Q1

Tool/software:

HI TI Teams

As shown in the attached diagram, the datasheet mentions that it can pass Level IV.

If the goal is to pass Level V, are there any recommended countermeasures?

(Such as adding decoupling capacitors to the circuit, incorporating LFP, or reducing the driver strength of the IC.)