Other Parts Discussed in Thread: TCA9617B

Tool/software:

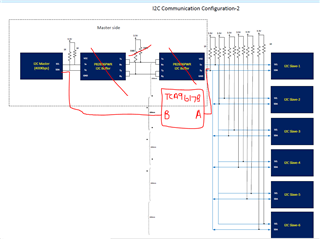

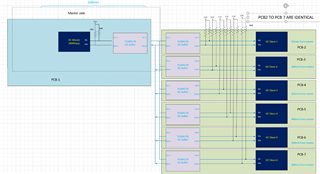

Master will communicate with 6 slaves through I2C buffer(P82B96PWR), each slave is at a distance of 100mm from the master, last slave is at a distance of 600mm. Master is in one PCBA and all slaves are interconnected through board to board connector .

1) Please suggest which configuration of BUFFER is works better?i2C Config-two options-for Ti Application Eng.pdf

2) Need P82B96PWR I2C buffer "pspice for Ti" or TINA simulation model to simulate the circuit.