Tool/software:

Hi, Sir,

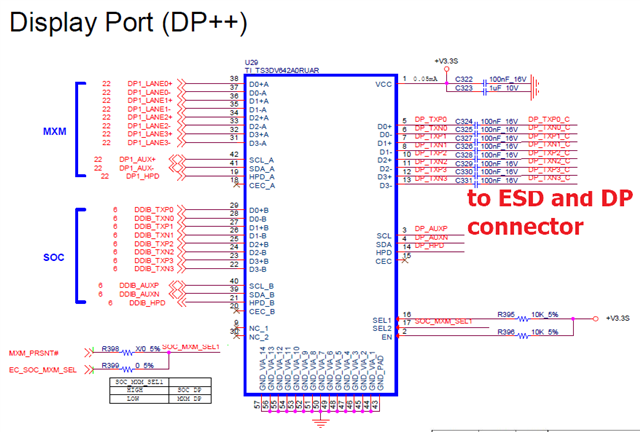

Our motherboard uses TI TS3DV642A0RUAR to switch DP signals from Raptor lake-U(SOC) and MXM module.

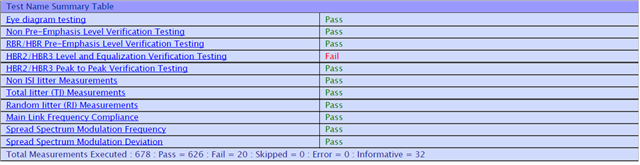

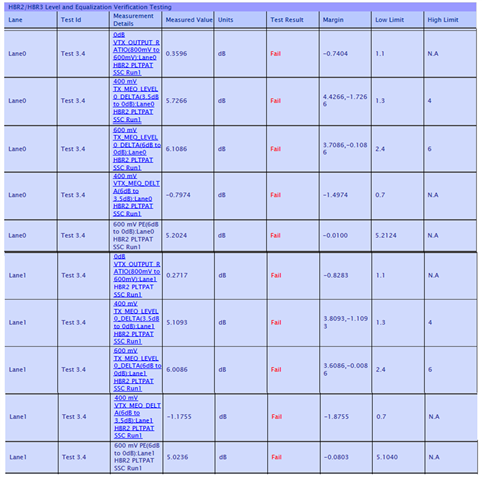

There are DP SI issues about HBR2/HBR3 Level and Equalization Verification Testing when we switch DP of Raptor lake-U.

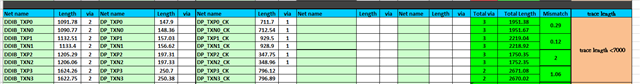

Because lengths of DP is not over Maximum length of Intel PDG. Those SI issues are likely not caused by signal attenuation.

Do you have any experience related to SI failure of HBR2/HBR3 Level and Equalization Verification Testing?

Could you provide any suggestions on how we can resolve this SI fail issue?

Do you have any recommendations for the length and number of vias from the TS3DV642A0RUAR to the DP connector?