Tool/software:

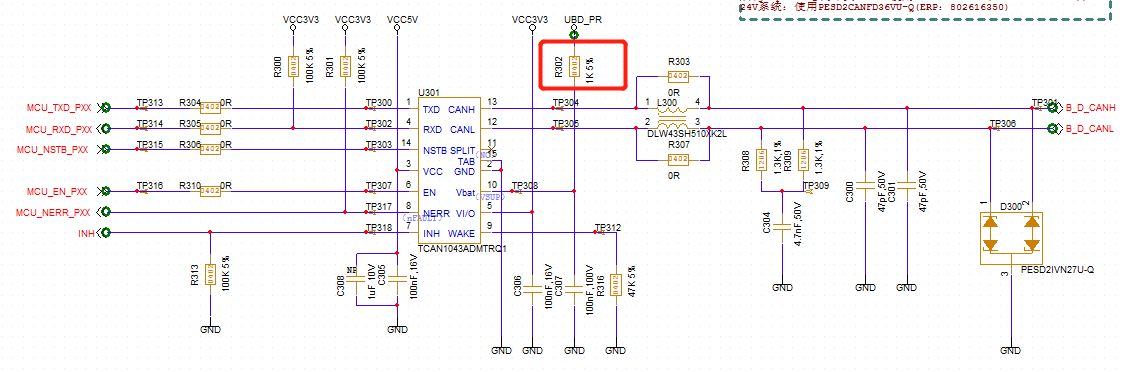

1.Considering that the Vsup voltage is high (the current requirement is less than 130uA), the fluctuation of Vsup may cause large crosstalk in adjacent signals, and 1k series resistance is generally considered (as shown in the figure below).

Then will the chip have a surge in Vsup current demand (large increment), making the chip Vsup below the undervoltage threshold?

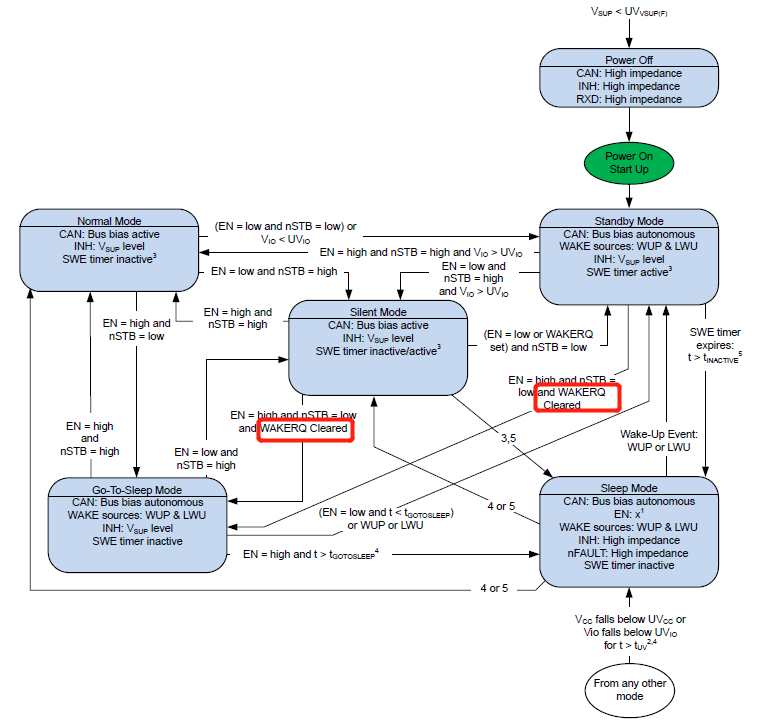

2.For sleep mode (caused by SWE timer overflow), tmode1 is the minimum time that the nSTB needs to remain low after the EN edge, but can the EN not perform a level shift (for example, EN (L→H )is required, and the EN is already low when it enters sleep)? Is this level switch before tmode1(red mask) necessary?

3.If the standby device enters the go-to-sleep system, WAKERQ is required to be cleared. However, the datasheet mentions that only UVCC/UVIO/transition to normal mode will clear WAKERQ.

However, considering that UVCC/UVIO causes CAN to become sleep-mode in any-mode, there is only one remaining way for WAKERQ to be cleared (that is, converting CAN to normal-mode), which contradicts putting CAN into go-to-sleep mode.So what to make of the WAKERQ clear?

4.The undervoltage of the VCC VIO needs to be undervoltage longer than the tUV. So voltage recovery also requires normal voltage to maintain tUV?

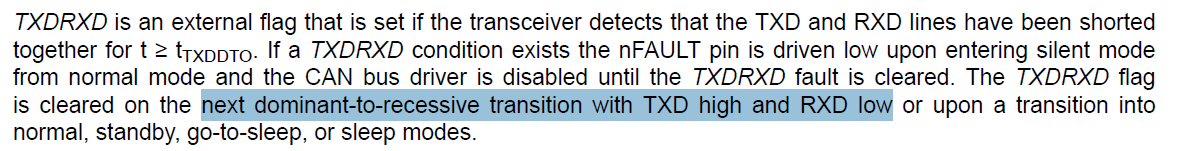

5.In the condition of TXDRXD flag clearing (8.3.7.1.7), the REC-DOM transition means that TXD is performing a REC-DOM transition? Or does it mean that a TXD or RXD performs a REC-DOM,transition?(that is, in silent-mode,a REC-DOM transition through the RXD (read-back bus) can pull up nFAULT by clearing the TXDRXD flag)?

6.PWRON, WAKERQ, and WAKESR are set for the first power-on.So for wake up source recognition, is the first power-on considered a local wake?

Besides, does initial power up means cold start?

7.There is a concept of "4 consecutive DOM-REC transitions" regarding the time requirement for clearing and setting bus fault flag bits, but the datasheet also gives tCBF data. There may be some difference between the two figures. Which one shall prevail?

(For example, if the 8-bit data switch 8M rate is used, the time of the 4 consecutive edges will be less than 1/8M*10^6*8=1us; The min of tCBF in the datasheet is 2.5us)