Tool/software:

Hello,

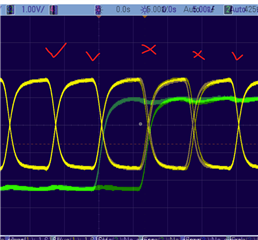

We're seeing an unexpected issue with the SN65LVDT33 part we are using on a board, where we are seeing higher-then-expected jitter on an output signal of the chip when sending a e.g. a 75Mhz clock through it (LVDS->SE):

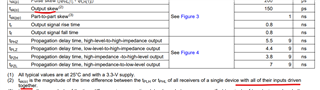

== SE output, containing +- 1ns jitter. (2 signals driven on chip)

== SE output, containing +- 1ns jitter. (2 signals driven on chip)

== LVDS input - very low jitter (2 signals driven on chip)

== LVDS input - very low jitter (2 signals driven on chip)

(We don't see this jitter on the LVDS coming in to the chip)

Interestingly enough, the jitter goes "away" if only one of the 4 channels of the chip is driven with this 75Mhz signal.

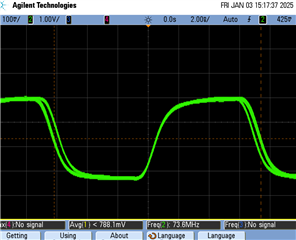

The scenario are now using to easily demonstrate this behavior, is to send a 10Mhz clock on one LVDS pair, and a 75Mhz clock on the second (yellow).

After taking some more scope images, it becomes clear that the "glitching" on the 75Mhz line occurs specifically when the other 10Mhz line (green) is going through a rising edge transition.

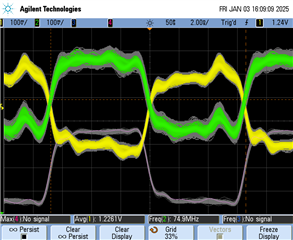

The below image was capture triggering on the rising edge of the slow signal, and is overlayed onto itself and shifted in paint. You can see how initially the 75Mhz periods are very clean, and at the moment when the rising edge of the slow/green "couples in", the rising edge of the 75Mhz signal is slightly delayed, causing the jitter effect (which is also seen above in the more simple scope image, "overlayed" by the scope itself, but not showing the exact correlation with the other signal).

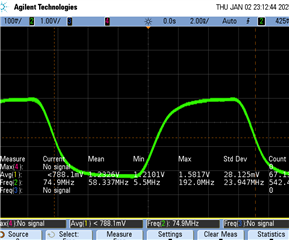

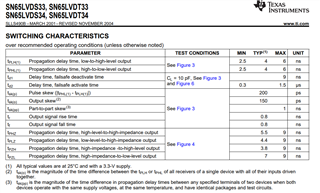

The datasheet lists the following limits

Practically, we had expected some jitter around the order of 150ps - not the 1000 ps we are seeing now.

Is this a known limitation?This behavior is somewhat suprising to us.

Thanks in advance for your feedback!

Kind regards,

Arnout