Tool/software:

Datasheet is saying follow,

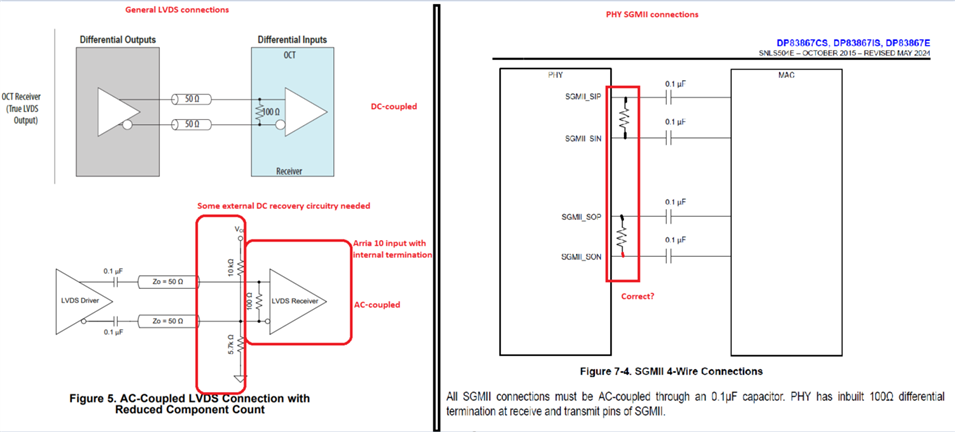

1. All SGMII connections must be AC-coupled through an 0.1μF capacitor.

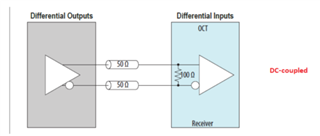

2. PHY has inbuilt 100Ω differential termination at receive and transmit pins of SGMII.

Questions:

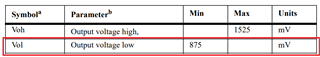

1. What is the reason why AC-coupling is required?

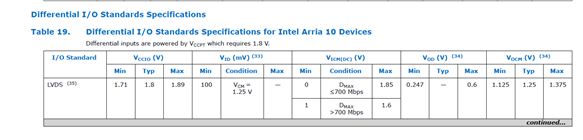

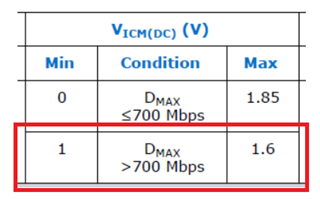

We are using Arria 10 GX and it's "normal LVDS" banks. Normal banks does not have and thus we need DC restore circuit to make sure that Vcm requirements are full-filled.

This is not so easy since PHY has inbuild 100ohm differential termination at receive and transmit side.

2. Any recommendation what kind of DC restore circuit would work?