- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Hi Ryan,

I got the S parameters of TS3DV642-Q1 from you two months ago. I have some questions, would you please help confirm it ASAP? we really need to make the S parameters clear to proceed with our simulation.

We are going to use TS3DV642RUATQ1 for MIPI CDPHY application and CDPHY exist at the same switch.

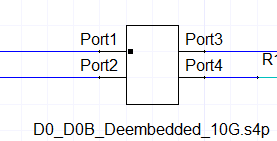

1) could you please clarify each port connection? Below shows your S parameter, but we do not know which port should be connect to D0+、D0-、D0+B、D0-B.

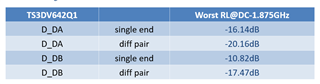

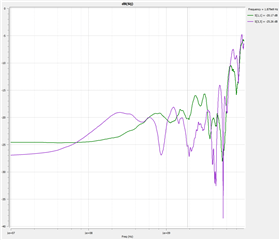

2) Below shows the summary for the S parameters, would you please let me know why the sing end performance is so worse? As for CPHY which is single end, we need the RL meet customer's spec.

3) What's the set up to get the S parameters? Would you please share me with the EVB board deign file and the simulation model? We want to know if our set up is same with yours.

Hi Ryan,

I'd like to add another question.

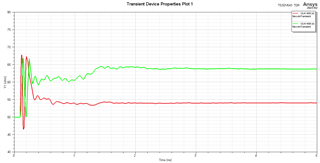

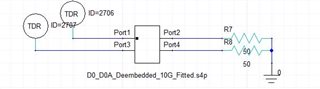

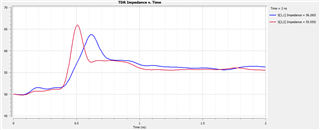

4) Below shows the TDR diagram and the simulation model, TS3DV642RUATQ1 only, using your S parameter. Customer requires us to show the TDR of the full path (ATE load board plus TS3DV642RUATQ1) , however we get a very terrible TDR diagram if adding TS3DV642RUATQ1. We guess there is some problems of your TDR, maybe because less sampling points at the low frequency.

question a: would you please send me the correct S parameter to help us to get a correct TDR diagram?

question b: would you please clarify if the best performance of this switch is with 50ohm impedance control on the ATE load board?

The version of the S parameters at our hand is 8750.TS3DV642Q1_s4p_10G.7z.

Hi Aimee,

1) could you please clarify each port connection? Below shows your S parameter, but we do not know which port should be connect to D0+、D0-、D0+B、D0-B.

For this S-Param, Port 1 connects to port 2, and Port 3 connects to port 4. + lanes can be used for Port 1 to Port 2, - lanes can be used for Port 3 to Port 4.

2) Below shows the summary for the S parameters, would you please let me know why the sing end performance is so worse? As for CPHY which is single end, we need the RL meet customer's spec.

I can test on my side to check, though I think the issue may just be setup. This S-parameter should be relatively accurate.

3) What's the set up to get the S parameters? Would you please share me with the EVB board deign file and the simulation model? We want to know if our set up is same with yours.

I can share the EVM design files, sure. However, this S-parameter I sent you is the only s-parameter model we have available. As long as you have port 1 to port 2 and port 3 to port 4, you should expect the correct performance.

4) Below shows the TDR diagram and the simulation model, TS3DV642RUATQ1 only, using your S parameter. Customer requires us to show the TDR of the full path (ATE load board plus TS3DV642RUATQ1) , however we get a very terrible TDR diagram if adding TS3DV642RUATQ1. We guess there is some problems of your TDR, maybe because less sampling points at the low frequency.

question a: would you please send me the correct S parameter to help us to get a correct TDR diagram?

question b: would you please clarify if the best performance of this switch is with 50ohm impedance control on the ATE load board?

The version of the S parameters at our hand is 8750.TS3DV642Q1_s4p_10G.7z.

This s-parameter is the the only one we have available for this device, however, the TDR should be accurate. I am double checking whether 50 Ohm impedance is correct or not.

Thanks,

Ryan

Hi Aimee,

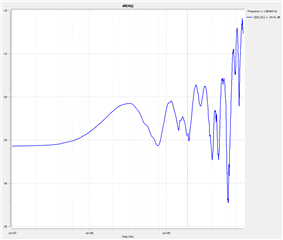

I'm simulating the S-parameter for D0_D0A and am not seeing performance issues. For example, I see -20.17dB and -25.26dB single-ended return loss at 1.875GHz and -24.41dB differential return loss at 1.884GHz. Is there a specific lane you're seeing performance issues on?

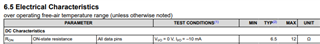

I also ran the TDR on this S-parameter file and got the following plot. The single ended impedance should be 50 ohms + the Ron of the MUX. In my simulation, the single ended impedance was closer to 56ohms

This makes sense since the TS3DV642-Q1 has a typical Ron around 6.5ohms

Best,

Shane