Tool/software:

hi TI expert,

I following the guide (PDK API Guide) to add a new Ethernet PHY and driver.

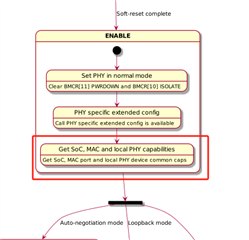

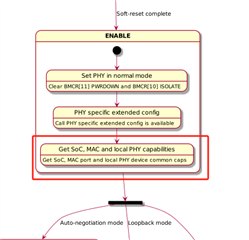

However, it seems stuck in ENABLE status due to "caps"

Is there any config or init missing?

Thank you for your assistance.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

hi TI expert,

I following the guide (PDK API Guide) to add a new Ethernet PHY and driver.

However, it seems stuck in ENABLE status due to "caps"

Is there any config or init missing?

Thank you for your assistance.

Hi WeiTing,

Can you please reach out to TDA4AL team on this question. DP83TG721 supports only FD1000 (Full Duplex 1000Mbps) and does NOT support auto-negotiation. They can help add these capabilities.

Thanks,

David

Hi David,

Yes, we want to apply FD1000 (Full Duplex 1000Mbps) on our project.

I had check mii_reg_f Register, the result is same as default(0x0).

Is there any config that I missing such that the Register is still 0x0?

Hi WeiTing,

Can you please reach out to the TDA4AL team on this, they will be better able to assist.

DP83TG721 capabilities are shown in register 0x1012. Your software is likely showing capability as "none" because DP83TG720 does not support standard ethernet, as shown in register 0xF.

Thanks,

David

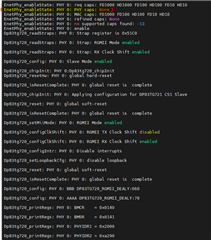

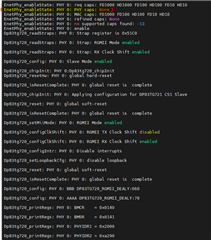

After bypass check cap at reg(0x0f) & change the data in dp83tg720 driver (dp83tg721_cs1_slave_init), it seems linked.

However, still cannot ping to the MCU.

Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G 0 Select MAC port 0: ENET_MAC_PORT_1 - RGMII 0 EnetBoard_setupPorts: 1 of 1 ports configurations found CPU Load: 100% Starting lwIP, local interface IP is 192.168.1.200 EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:0 From 1 To 0 EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:4 From 1 To 0 EnetMcm: CPSW_2G on MCU NAVSS Mdio_open: MDIO manual mode enabled PHY 0 is alive Cpsw_openPortLink: Cpsw_openPortLink EnetPhy_bindDriver: PHY 0: OUI:080028 Model:29 Ver:00 <-> 'Dp83tg720' : OK Host MAC address: 64:1c:10:22:72:35 [LWIPIF_LWIP] Enet LLD netif initialized successfully status_callback==UP, local interface IP is 192.168.1.200 Enet lwIP App: Added Network IP address I/F ti0: 192.168.1.200 Initializing apps UDP server listening on port 5001 Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0004 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x0000 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0000 Dp83tg720_printRegs: PHY 0: REG19 = 0x0000 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0004 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x0000 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0000 Dp83tg720_printRegs: PHY 0: REG19 = 0x0000 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable CPU Load: 3% Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0004 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x0000 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0000 Dp83tg720_printRegs: PHY 0: REG19 = 0x0000 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0004 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x0000 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0000 Dp83tg720_printRegs: PHY 0: REG19 = 0x0000 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable CPU Load: 3% Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0004 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x0000 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0000 Dp83tg720_printRegs: PHY 0: REG19 = 0x0000 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable

Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G Wrong peripheral type, enter again Select peripheral type 0: CPSW_2G 0 Select MAC port 0: ENET_MAC_PORT_1 - RGMII 0 EnetBoard_setupPorts: 1 of 1 ports configurations found CPU Load: 100% Starting lwIP, local interface IP is 192.168.1.200 EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:0 From 1 To 0 EnetAppUtils_reduceCoreMacAllocation: Reduced Mac Address Allocation for CoreId:4 From 1 To 0 EnetMcm: CPSW_2G on MCU NAVSS Mdio_open: MDIO manual mode enabled PHY 0 is alive Cpsw_openPortLink: Cpsw_openPortLink EnetPhy_bindDriver: PHY 0: OUI:080028 Model:29 Ver:00 <-> 'Dp83tg720' : OK Host MAC address: 64:1c:10:22:72:35 [LWIPIF_LWIP] Enet LLD netif initialized successfully status_callback==UP, local interface IP is 192.168.1.200 Enet lwIP App: Added Network IP address I/F ti0: 192.168.1.200 Initializing apps UDP server listening on port 5001 Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete EnetPhy_enableState: PHY 0: enable Dp83tg720_readStraps: PHY 0: Strap register is 0x51C0 Dp83tg720_readStraps: PHY 0: Strap: RGMII Mode enabled Dp83tg720_readStraps: PHY 0: Strap: RX Clock Shift enabled Dp83tg720_config: PHY 0: Slave Mode enabled Dp83tg720_chipInit: PHY 0:Dp83tg720_chipInit Dp83tg720_resetHw: PHY 0: global hard-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_chipInit: PHY 0: Applying configuration for DP83TG721 CS1 Slave Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_setMiiMode: PHY 0: RGMII Mode enabled Dp83tg720_configClkShift: PHY 0: RGMII TX Clock Shift disabled Dp83tg720_configClkShift: PHY 0: RGMII RX Clock Shift enabled Dp83tg720_configIntr: PHY 0: Disable interrupts Dp83tg720_setLoopbackCfg: PHY 0: disable loopback Dp83tg720_reset: PHY 0: global soft-reset Dp83tg720_isResetComplete: PHY 0: global reset is complete Dp83tg720_printRegs: PHY 0: BMCR = 0x0140 Dp83tg720_printRegs: PHY 0: BMSR = 0x0141 Dp83tg720_printRegs: PHY 0: PHYIDR1 = 0x2000 Dp83tg720_printRegs: PHY 0: PHYIDR2 = 0xa290 Dp83tg720_printRegs: PHY 0: PHY_GIGESR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYSTS = 0x0084 Dp83tg720_printRegs: PHY 0: PHYCR = 0x000b Dp83tg720_printRegs: PHY 0: MISR1 = 0x4400 Dp83tg720_printRegs: PHY 0: MISR2 = 0x0000 Dp83tg720_printRegs: PHY 0: RECR = 0x0000 Dp83tg720_printRegs: PHY 0: BISCR = 0x0100 Dp83tg720_printRegs: PHY 0: MISR3 = 0x0800 Dp83tg720_printRegs: PHY 0: REG19 = 0x0400 Dp83tg720_printRegs: PHY 0: CDCR = 0x0000 Dp83tg720_printRegs: PHY 0: PHYRCR = 0x0000 Dp83tg720_printRegs: PHY 0: SGMII_CTRL = 0x007b Dp83tg720_printRegs: PHY 0: RGMII_CTRL = 0x0128 Dp83tg720_printRegs: PHY 0: RGMII_DELAY_CTRL = 0x0002 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_CONTROL = 0x8001 Dp83tg720_printRegs: PHY 0: MMD1_PMA_PMD_EXT_CASP = 0x0002 EnetPhy_enableState: PHY 0: req caps: FD1000 EnetPhy_enableState: PHY 0: PHY caps: FD1000 EnetPhy_enableState: PHY 0: MAC caps: FD1000 FD100 HD100 FD10 HD10 EnetPhy_enableState: PHY 0: refined caps: FD1000 EnetPhy_enableState: PHY 0: PHY is not NWAY-capable Cpsw_handleLinkUp: Port 1: Link up: 1-Gbps Full-Duplex MAC Port 1: link up link_callback==UP CPU Load: 3%

Hi WeiTing,

Glad to hear the PHY appears linked after bypassing the cap at reg 0xF. Can you read register 0x1 and ensure bit[2] equals 1?

Which MAC interface are you using? Can you please share the schematic? If link is up but communication is not possible, this generally points to an issue with the MAC interface configuration.

Thanks,

David

Hi David,

Can you read register 0x1 and ensure bit[2] equals 1?

-> Reg 0x01 value is 0x0145 after RTOS indicates phy status is linked.

-> Additionally, Reg 0x10 value is 0x0605.

-> Both regs indicate link is up.

Which MAC interface are you using?

-> we want to use RGMII interface.

Can you please share the schematic?

-> my colleague previously posted the schematic related to the PHY chip. I'm not sure if this is sufficient.

Hi WeiTing,

Glad to hear that link is up. The MAC interface may be the limiting factor here then. I see RX shift mode is enabled and TX shift mode is disabled.

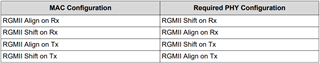

Can you verify on the MAC side that RX shift mode is disabled and TX shift mode is enabled? Below is the required configuration.

Thanks,

David

Hi David,

I couldn’t find the MAC side RX/TX shift mode configuration, so I reached out to the TDA4AL team. I’m still waiting for their reply.

In the meantime, I came across this post(e2e link) about configuring rx/tx shift mode in MAC.

Following its suggestion, I tried commenting out the code for RGMII TX delay, the result is same as two days ago(phy is linked, but unalbe to ping).

Additionally, I found another post discussing RX clock configuration.(disscuss about config rx clk) In that post, it was mentioned that the TX/RX clock on the TDA4 side can be configured in the PHY via RGMII Control Register (RGMIICTL) & Reg addr 0x86 - RGMII Delay Control Register (RGMIIDCTL)

I’m confused by this statement.

Does this mean that the RGMIICTL and RGMIIDCTL registers can configure RGMII on the MAC side, and the PHY’s RX/TX clock is configured using GPIOs?

Looking forward to your clarification.

Hi David,

after struggle a day, I try few couple set about rx/tx shift mode and RTOS MAC side TX/RX shift mode setting.

Finnally, It's work!!

Thank you, David.