Part Number: DS32EL0124

Other Parts Discussed in Thread: LMH0341, , DS25BR100, DS32ELX0124, LMH0397, DS90UB913A-Q1

Tool/software:

Hi ,

First, I have to mention that this query is general and not specific to the chip in the title.

Ti does not provide a way to ask an E2E question without choosing the device.

So please forward this request to support that that specialize in broad number of devices by Ti and not only this SERDES.:

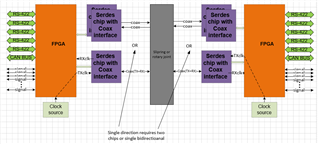

I am Looking for TI Chip that will best fit to the following application. (see attached block diagram)

The requirement is to pass different signals with different bandwidth and asynchronous to each other, on a single coax. The way is to aggregate them and pass then on single Coax cable that farther on will pass via rotary joint or slip ring devices. Thus, reducing the rotary joint and slipring size/nodes/cost comparing to passing them without the aggregation.

.

It is preferable to have the chip to be bidirectional so to have TX and RX on the same coax. So that single coax will be used.

The maximum aggregate rate can be less then 200Mbps but prefer to have 1G to 3Ghz rate.

I have added the block diagram of the solution that based on FPGA that on the TX side samples the signals/buses and put them on a single output. That output together with clock will be fed to TI chip that you will recommend me and will interface to the coax cable.

On the Rx side the chip will receive the data from the coax cable and provide the FPGA with the recovered data and recovered clock , the FPGA will extract the data from the aggregate input and recover all the signals.

The length of the cable is max 3 m. But I will prefer the chip to have pre-emphasis and on the receive side equalizer.

Also, in order to have eliminate DC on the line scrambler and de-scrambler is needed.

Please suggest a chip (for Tx, and for RX) that can best fit to this application.

(chips that I have check but not really fit are the : DS32EL0124 , DS32ELX0124, LMH0341/041/071/051 or the LMH0397, DS25BR100 none of them seems to match)

Note that the application requires clock to sample the incoming signals and need to be recovered on the other side, That is the reason that I hardly see the FPD link 3 serializer DS90UB913A-Q1

As a candidate)

Also note that the application is not for video transfer and the aggregated data is not coded at all. (for example, it is not SMPTE compliant)

Thanks,

Avner