Other Parts Discussed in Thread: HD3SS3411, TS3USB31E, TMUXHS221, HD3SS3212, TS3USB221, HD3SS6126

Tool/software:

Hello,

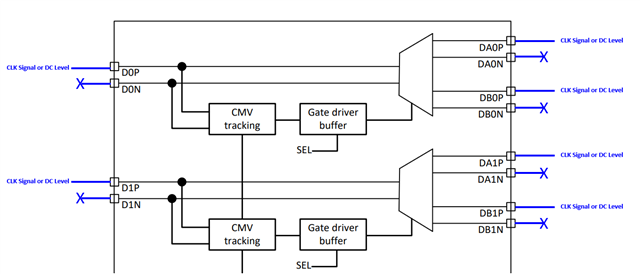

This is an inquiry regarding the usage of the TMUXHS4412 Single-Ended.

We are considering using it in connection with the FPGA's IO channels.

Depending on the operational functions of the FPGA, we are planning to use the same channel as shown in the image below. Could you please confirm if this is possible?