Other Parts Discussed in Thread: DP83TC812R-Q1, DP83TC812S-Q1

Tool/software:

Hello team,

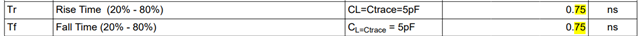

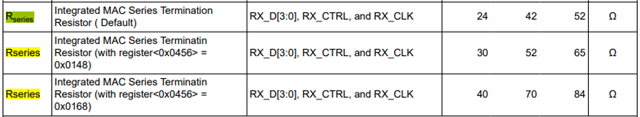

For the rise time, customers want to know the concrete range within different condition, for example:

1. Under different drive level

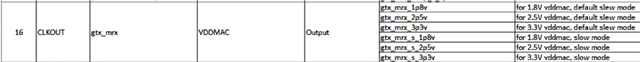

2. Customer wants to use 3.3V for VDD IO, will the rise time be influenced? Is the maximum value still 0.75ns?

Thanks!

Regards,

Daniel Wang