Part Number: LMH1228

Other Parts Discussed in Thread: LMH1297EVM, LMH1297

Tool/software:

Hello everyone!

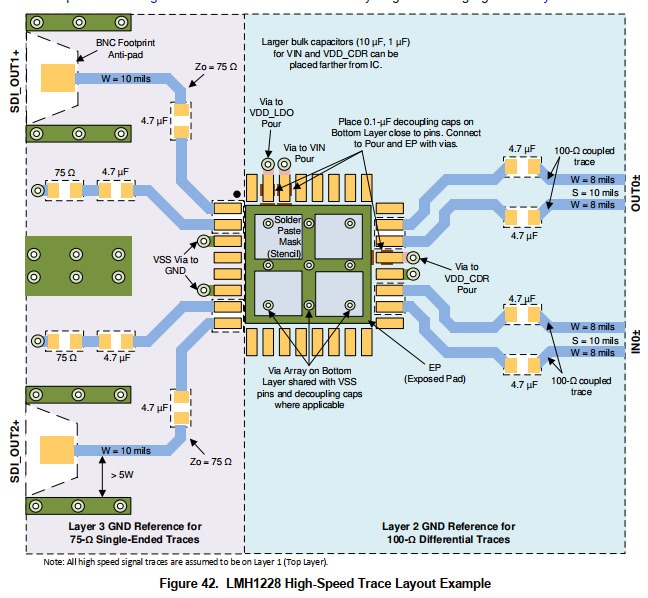

I'm develop a project using LMH1228 and I noted that in the page 36, Layout Example on datasheet, is drawing the isolated area for BNC connector with green areas arround.

Generaly the BNC connctor has external enclousure grounding in the PCB with the ground plane, but in draw that I mentioned above I'm doubit where the BNC ground is conected?

Somebory can help me please?

Thanks

GND1

GND1 VDD1

VDD1