Other Parts Discussed in Thread: DP83867E

Tool/software:

I enabled SGMII interface and set PHY as autonomous mode, but the PHY can not finish auto-negotiation while link is up.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I enabled SGMII interface and set PHY as autonomous mode, but the PHY can not finish auto-negotiation while link is up.

Hi Philip,

I want to clarify:

1. Autonomous Mode is not the same as autonegotiation. Autonomous mode means the PHY will automatically enter link up upon power up. When autonomous mode is disabled, you need to write to register 0x18B to enable link up. Auto-negotiation is a handshake process to determine the speed/duplex mode of the PHY.

2. The DP83TG720 does not support MDI autonegotiation, but it supports SGMII autonegotiation.

When you say the PHY cannot finish auto negotiation while link is up, do you mean MDI or SGMII autonegotiation? Are you reading a particular PHY register?

Here is our SGMII troubleshooting guide for reference, can you poll the SGMII registers mentioned here: https://www.ti.com/lit/an/snla473/snla473.pdf?ts=1737586726526

Best regards,

Melissa

Hi Melissa,

I would like to know if the DP83867E/IS/CS supports MDI auto-negotiation, or SGMII auto-negotiation, or both? When I developed the driver for DP83867E/IS/CS, due to some reason, the SGMII interface of MCU cannot work, but the auto-negotiation still can pass. If the PHY has SGMII auto-negotiation, and the SGMII interface of MCU cannot work, why can the auto-negotiation complete? So, I thought, auto-negotiation is performed only between PHYs. Is auto-negotiation mechanism of DP83TG720 different from the one of DP83867E/IS/CS?

Thanks,

Best regards,

Philip

Hi Philip,

Are you working on both the DP83TG720 and DP83867 in your design?

The DP83867 supports both MDI and SGMII auto negotiation.

The DP83TG720 supports only SGMII auto negotiation.

SGMII autonegotiation is specified in the SGMII Standard, and I also describe the mechanism in the app note I linked.

MDI auto neogitation is specified by the IEEE802.3 standard. It is a process where the PHY and link partner exchange capabilities to determine speed and duplex mode.

If you are having trouble with the DP83867 connecting to the MAC via SGMII, I recommend trying the steps mentioned in section 1.1, 1.2 and 1.3. Please confirm once you have been able to try this. https://www.ti.com/lit/an/snla473/snla473.pdf?ts=1737586726526

Best regards,

Melissa

I don't have trouble with the DP83867. I only have trouble with the DP83TG720. I meant I can use the DP83867 to do auto negotiation and get a suitable speed by using MDC&MDIO while SGMII interface is disable. I found there are auto-negotiation and SGMII auto-negotiation in the datasheet of DP83867. In my previous project, I used auto-negotiation complete flag to check if the PHY has finished auto-negotiation not SGMII auto-negotiation complete flag. I would like to know if they are different. If they are different, what is the difference between them? I also found there is only SGMII auto-negotiation appearing in the datasheet of the DP83TG720. I also would like to know when we use SGMII auto negotiation and when we use auto negotiation?

Hi Philip,

MDI auto-negotiation is not available on DP83TG720. You may check for link status in register 0x1 bit[2].

SGMII link status can be monitored in register 0x60A bit[11].

Thanks,

David

Hi David,

I checked for link status in register 0x01 bit[2] , which is high and SGMII link status in register 0x60A bit[11], which is low. It means link status is up and SGMII link status is down. How can I solve the issue?

Thanks,

Philip

Hi Philip,

To help with further debug, please reference the app note at the following link: https://www.ti.com/lit/pdf/snla473

Can you please check the following:

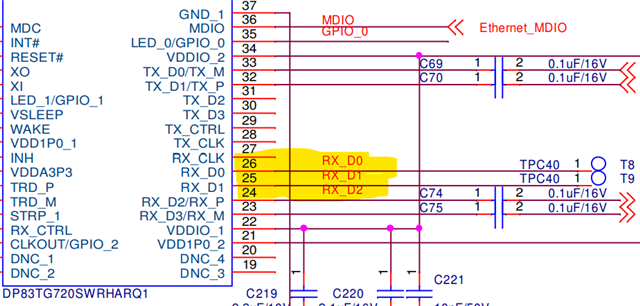

Is the PHY configured for SGMII via bootstrap? Please provide the configuration for pins 24, 25 and 26. The default state for SGMII is for these pins to be floating.

Please check the SGMII_CTL_1 register status(Register offset 608h), in particular bit 9 (cfg_sgmii_en) to see if SGMII is enabled. Also, please check bit 0 of the same register, this bit should normally be set to 1 to enable SGMII auto-negotiation.

Also, do you have schematics you can provide to review?

Regards,

Undrea

Hi David,

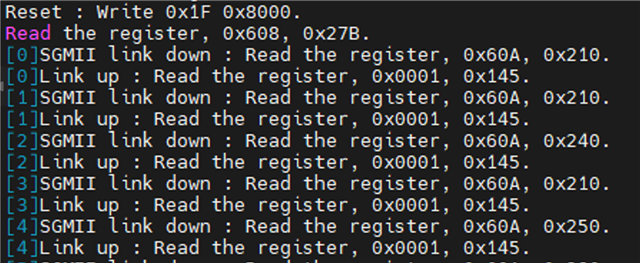

The above picture shows the register 0x608, where the bit 9 and the bit 0 are both 1.

The above picture is our schematic for DP83TG720, where the pin 24, 25, and 26 are all floating.

Thanks,

Philip

Hi Philip,

What is the processor you are using?

Is auto negotiation enabled in the processor?

Do you have the driver .c code we can review?

Regards,

Undrea

Dear Undrea,

The processor we using is zynq ultrascale+ mpsoc.

I am not sure if it enables the SGMII auto negotiation.

What if the processor doesn't support the SGMII auto negotiation?

Could we finish the SGMII auto negotiation for the DP83TG720 only using the MDC&MDIO interface?

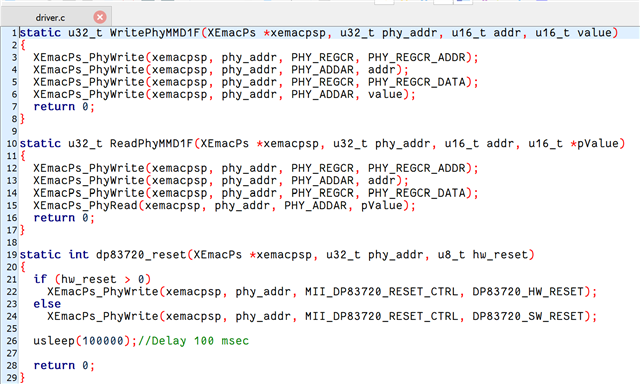

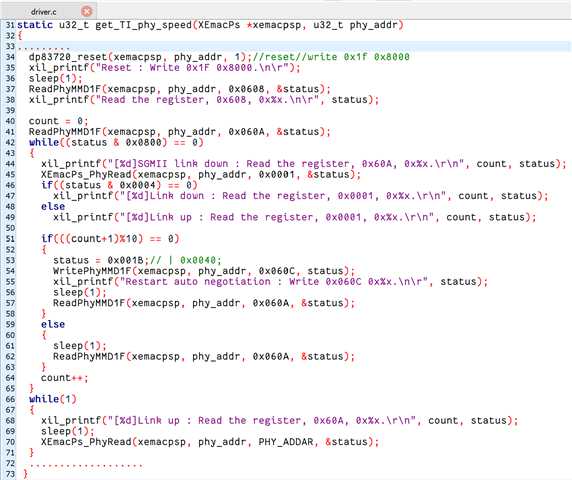

driver.c :

Thanks,

Philip

Hi Philip,

I am consulting with the team and will get back to you by tomorrow.

Regards,

Undrea

Hi Philip,

Since the processor does not support auto-negotiation, we recommend disabling auto-negotiation in the PHY. SGMII Auto-Negotiation can be disabled by setting bit[0] = 0b0 in the SGMII Configuration Register (SGMIICTL, address 0x608).

Also, in the driver code to reset the PHY can you change to a Soft Reset (Reg 0x1F, bit 14).

Note, although we are removing the auto-negotiation, the code above appears to write the default value of this register and has the value to restart SGMII auto-negotiation (0x0040) commented out.

Regards,

Undrea

Hi Undrea,

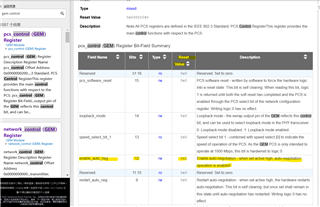

In our platform, there is a register with sgmii_en bit, whose description is shown below :

Surf the link https://docs.amd.com/r/en-US/ug585-zynq-7000-SoC-TRM/Register-XEMACPS_NWCFG_OFFSET-Details for details.

Does it mean the SGMII of the MCU supports auto negotiation?

Thanks,

Philip

Hi Philip,

I don't see anywhere in the document that explicitly states SGMII auto-negotiation is supported. As pointed out in a related document, when SGMII is enabled, there is no auto-negotiation. I take the register description above to mean that the controller changes what is advertised(From auto-negotiation enabled to disabled as it would be enabled in RGMII). It would be best to check directly with AMD.

Were you able to try the changes suggested last week?

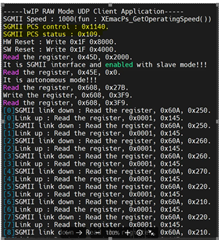

Dear Undrea,

I tried the changes suggested last week, but the SGMII link status is still down.

The procedure is as below :

1. write the value, 0x4000, to the register, 0x1F.

2. write the value, 0x0278, to the register, 0x608,

3. read the value form the register, 0x60A, and check the bit 11 of the value.

I kept read the register, 0x60A, and check the bit 11 every second, but it was still low.

I found the the other register, which is shown below and shows the auto negotiation status.

![]()

The link of the above register is : https://docs.amd.com/r/en-US/ug1087-zynq-ultrascale-registers/pcs_control-GEM-Register

I read the register, SGMII PCS control, and the value in the register is 0x1140(= 0001_0001_0100_0000) as shown below.

Althogh the bit 12 of the register is high, which shows auto-negotiation of the MCU is enabled, the SGMII is still down.

Thanks,

Philip