Part Number: DP83867IR

Tool/software:

Hello,

My customer is facing issue that they rarely can NOT read data via MDIO.

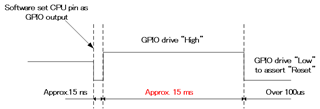

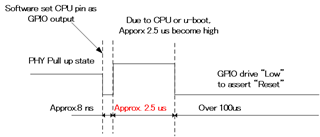

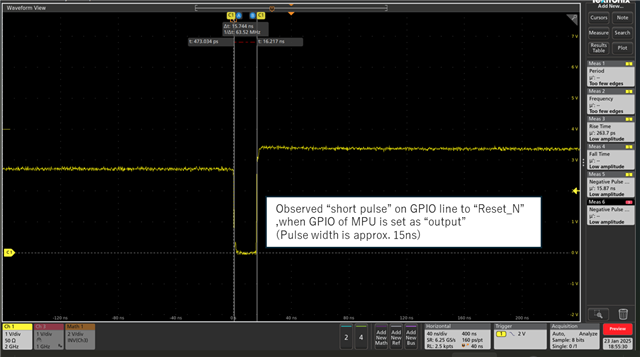

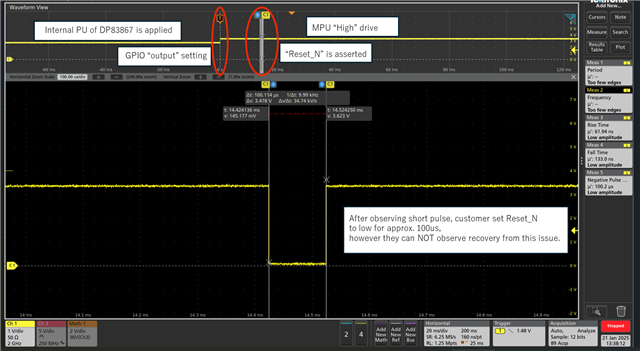

According to their investigation, they observed short pulse from MPU GPIO line to "Reset_N" of DP83867IR when they set MPU pin to GPIO output as shown below.

After observing this short pulse, even though they set "Reset_N" to low for 100 us, this issue is NOT recovered.

Then, customer have following questions.

Q1. According to dataheet you described as shown below for "Reset_N".

"The RESET input must be held low for a minimum of 1µs."

However, if user input such short "low" pulse to "Reset_N", is there possiblity that device cause such phenomenon ?

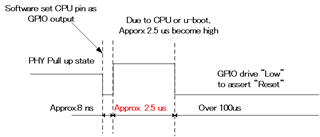

Q2. Customer change circuit. They implement 2.2kohm PD on "Reset_N" line to nullify effect of internal PU of "Reset_N" pin of DP83867.

After that, they have never observed above issue. However they would like to know your opinion about this workarroud.

Could you give your feedback about this workaround ?

Best Regards,