Part Number: TCAN1145-Q1

Tool/software:

Hi Team,

As I see in the manual, the PWRON is set when the device is powered on from battery, also when the power on reset POR is triggered.

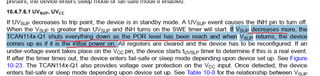

Does this flag also set when the UVsup event take place?

Regards,

Punith Chandra