Part Number: DS90UB954-Q1

Tool/software:

Hi Team,

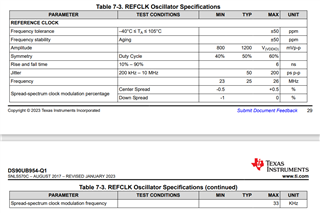

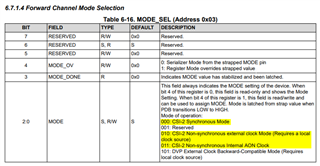

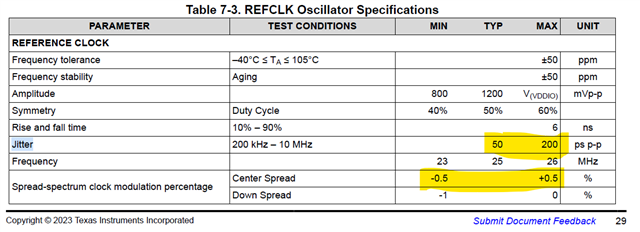

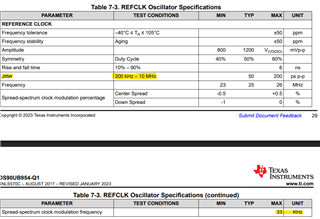

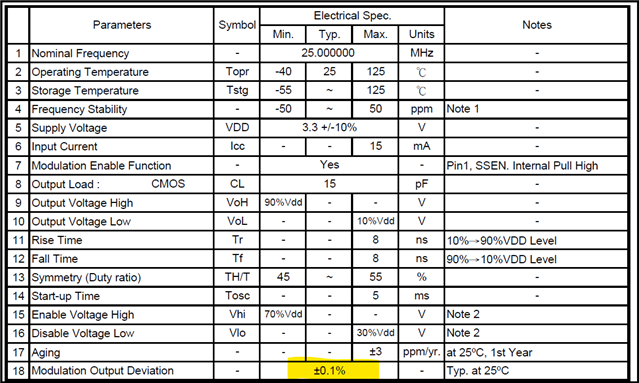

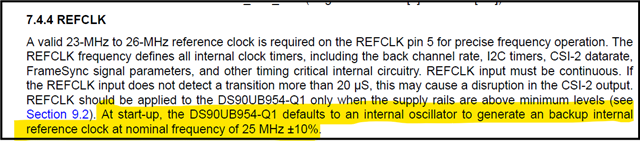

As per the datasheet of DS90UN954-Q1, it internally generates 25MHz clock initially as a backup. We are using in synchronous mode.

Is there a way, we can use DS90UB954-Q1 from internal oscillator only? I want to remove to external resonator.