Tool/software:

Hello,

we are using DP83822 and we notice active "next page" bit on the autonegotation bitstream.

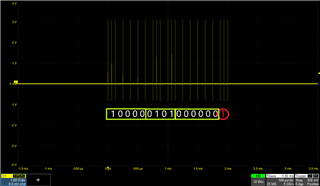

Here is measured bitstream from DP83822

Last bit is "next page" and it is "1". But in register 0x0004 (Auto-Negotiation Advertisement Register (ANAR)) we have "0".

Why MAC send "1" when we need "0" on this bit?

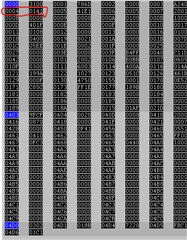

And here is dump of almost all registers (odds positions are register number, evens are value) Register 0x0004 is in red circle. Value in this reg is 0x0141 (next page bit == 0)

Thanks in advance,

Jiri