Part Number: DS90CR285

Other Parts Discussed in Thread: DS90CR286,

Tool/software:

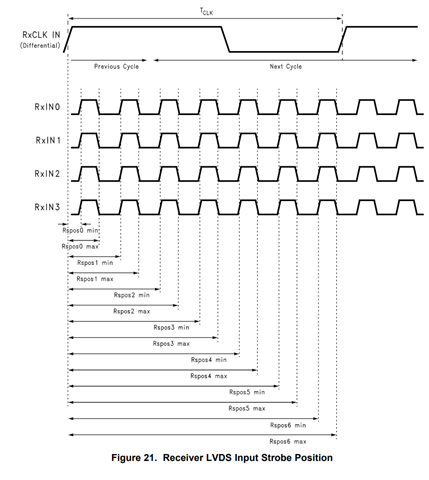

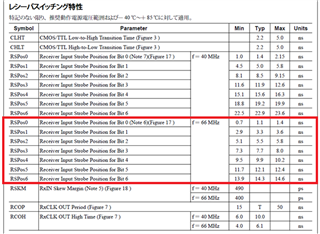

In the datasheet for the channel link IC device "DS90CR285, DS90CR286," the RSPos* for f=66MHz is listed in the red frame in the receiver switching characteristics below. The min and max values of the sampling points during this 7-bit transmission are specified in increments of 2.2nsec. However, at 66MHz, it is thought that the increments are 2.165nsec, and it is thought that the deviations will increase toward the latter half of the bit. (The deviation is about 0.21nsec for the 7th bit) As a result, it seems that the eye pattern is getting tighter in the latter half of the bit, as previously reported. This is listed as a rounded value as a standard value, and is it true that the receiving sampling point is actually a little further forward in the latter half of the bit?

Could you teach me ?

Thanks and best regards,

Daisuke Nomura