Tool/software:

Dear, support team.

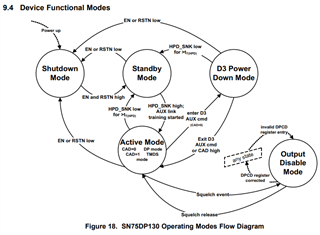

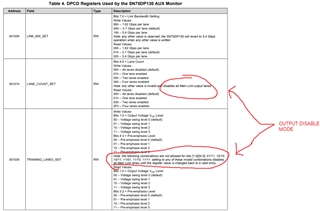

Q1. Conditions for transition to Output Disable Mode.

I understand that there are two conditions for transition to Output Disable Mode.

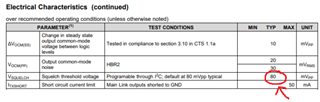

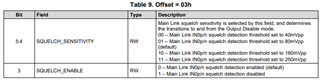

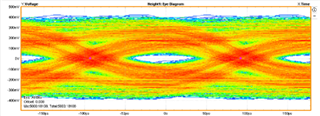

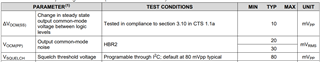

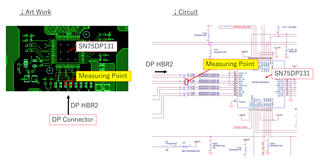

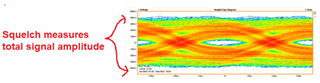

First. When a Squelch event occurs in the video signal.

When the values of DPCD registers 101h and 103h become invalid.

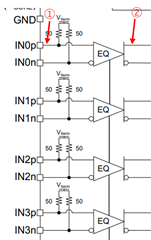

Second. When any of the main links 0 to 3 in use does not transmit the idle pattern and becomes disabled.

I believe that this is the condition that causes the second condition to occur.

Is my understanding correct?

Q2. Detecting Output Disable Mode.

Is there a way to check if the device state is in Output Disable Mode?

Best Regards,

Hiroaki Yuyama