Other Parts Discussed in Thread: DP83TG720R-Q1, DP83TG720EVM-MC, DP83TG720S-Q1

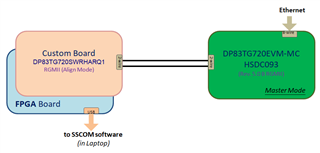

Our team is evaluating the DP83TG720R-Q1 Ethernet PHY using a custom-designed board and the DP83TG720EVM-MC evaluation board.

The setup is as follows:

- Evaluation Board (EVM) Connection: The DP83TG720EVM-MC is connected to Ethernet.

- Custom Board Setup:

- The custom board also uses the DP83TG720R-Q1.

- The custom board is connected to an FPGA, which serves as the MAC interface.

- The FPGA is connected to a laptop via USB, and SSCOM software is used to monitor communication.

- PHY ID Recognition:

- The PHY is correctly detected in SSCOM, meaning the MDIO interface is working.It gives following msg:

Configuring network interfaces...ZYNQ GEM: ff0e0000, mdio bus ff0e0000, phyaddr 0, interface rgmii-id

[17:32:49.368]IN¡û¡ô[ 7.669787] macb ff0e0000.ethernet eth0: PHY [ff0e0000.ethernet-ffffffff:00] driver [TI DP83TG720CS1.1] (irq=POLL)

[ 7.680170] macb ff0e0000.ethernet eth0: configuring for phy/rgmii-id link mode - However, communication does not happen, or if it does, it lasts for a very short time (~10 sec).

- The PHY is correctly detected in SSCOM, meaning the MDIO interface is working.It gives following msg:

- Error Message in SSCOM:

- [17:34:17.463] IN¡û¡ô [100.874880] macb ff0e0000.ethernet eth0: Link is Up - 1Gbps/Full - flow control off

- [17:34:27.681] IN¡û¡ô [105.994103] macb ff0e0000.ethernet eth0: Link is Down

This suggests that the link is initially established but drops shortly after.

TROUBLESHOOTING done so far:

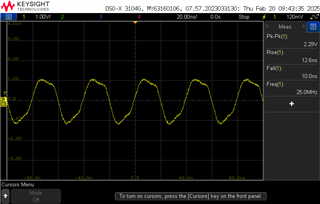

Clock Signal Verified

- The 25 MHz XTAL/Clock source has been checked for correct frequency, rise/fall times, load capacitance, and impedance matching.

PHY Address Identified

- The PHY ID is detected correctly via MDIO.

MDIO Communication Checked

- The FPGA successfully reads the PHY ID, confirming that MDIO and MDC signals are working, Isn’t it ?

Power and Voltage Levels Checked

- Verified that VDDIO(1.8V), VDDA3P3, and VDD1P0 are within the recommended range.

Strapping Pins and Configuration Verified

- Ensured correct bootstrap settings for PHY operation. I can also try other configuration if you have any other suggestion?

Termination Resistors Verified

- Confirmed that 100Ω differential termination is present between TRD_P and TRD_M.

-

QUESTIONS for TI Support Team:

Measured DC Voltage on TRD_P and TRD_M

- Found 1.65V instead of the expected ~1.1V, suggesting a potential issue with signal integrity.

PHY Link Stability Issue Observed

- The link is established but drops after ~10 seconds, as seen in the SSCOM log.

- Why does the link establish briefly (~10 sec) and then drop?

- Is a DC voltage of 1.65V on TRD_P/TRD_M abnormal? If so, what could be causing it?

- Could impedance mismatch or termination affect long-term link stability, even if the link initially establishes?

- Do we have to connect RESET_N and WAKE pin all the time to 1.8V and 3.3V respectively?

- Could this issue be related to FPGA MAC configuration? Are there specific settings needed for proper MAC-PHY interaction?

I have attached the schematic for your reference.

We would appreciate any insights or debugging suggestions from TI.

THANK YOU !