Tool/software:

Hi team,

In the datasheet’s section 8.2.2.2.1 MDI Layout Guidelines, it states, “MDI traces must be 50Ω to ground and 100Ω-differential controlled impedance.”

My customer is facing an issue where trying to meet both the 100Ω differential and 50Ω single-ended requirements results in a layout where the differential signal traces are spaced further apart compared to a layout with only 100Ω differential traces.

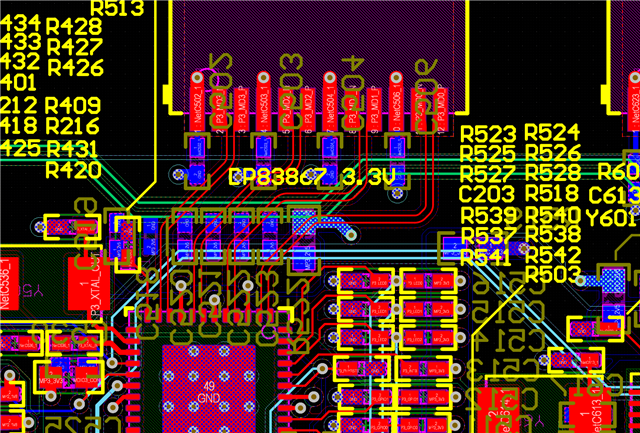

I would like to show the layout diagram of the DP83867E SGMII EVM as an example of a layout pattern. Could you provide this diagram?

Also, is there a priority among the three requirements: 100Ω differential, 50Ω single-ended, and the spacing between differential signal traces?

What is the acceptable design tolerance for the 100Ω differential and 50Ω single-ended impedance?

Best regards,