Other Parts Discussed in Thread: SN65DSI84

Tool/software:

Hi, TI expert

A customer has a question regarding the SN65DSI84-Q1 output.

- Application : Video splitter and channel display device

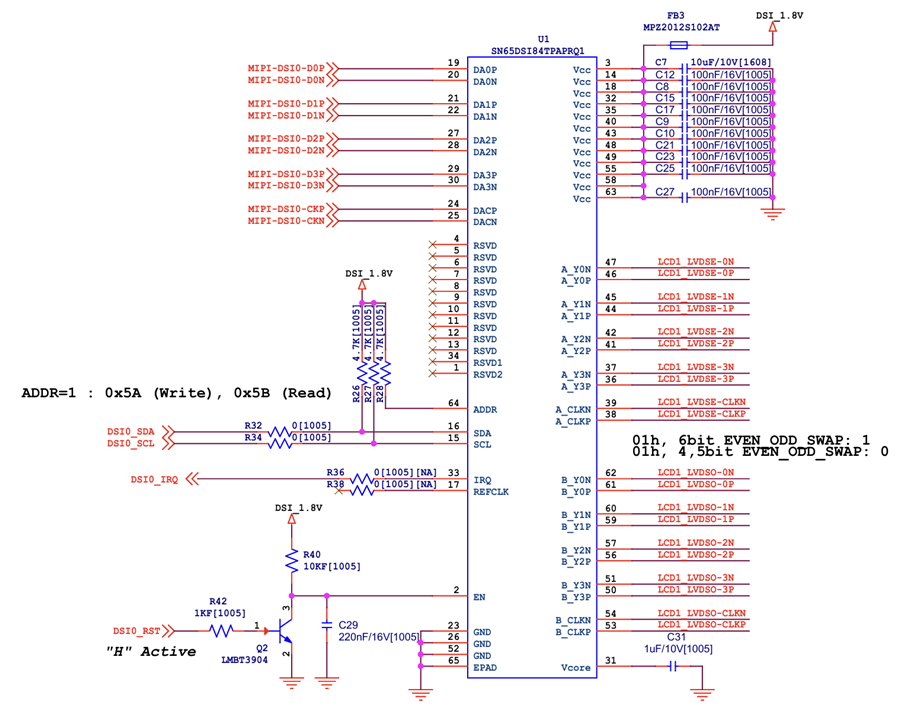

The current hardware configuration is as follows.

- RK3568 DSI Output (Single) -> SN65DSI84TPAPRQ1 (Dual LVDS Output) -> LCD PANEL (resolution 1920x360)

[Review and Issues]

1) When RK3568 DSI Output is set to 1920x1080, the screen is displayed normally on the LCD PANEL. (However, only the top 1/3 of the 1080 screen is displayed.)

2) When RK3568 DSI Output is set to 1920x360, the LCD screen is displayed abnormally (Please refer to the image below.)

The video display timing is as follows, and the SN65DSI84TPAPRQ1 setting value is attached.

clock-frequency = <142380000>;

hactive = <1920>;

hfront-porch = <60>;

hsync-len = <60>;

hback-porch = <60>;

vactive = <360>;

vfront-porch = <120>;

vsync-len = <530>;

vback-porch = <120>;

hsync-active = <0>;

vsync-active = <0>;

[Question]

Q1) Does SN65DSI84TPAPRQ1 not support 1920x360 resolution LCD?

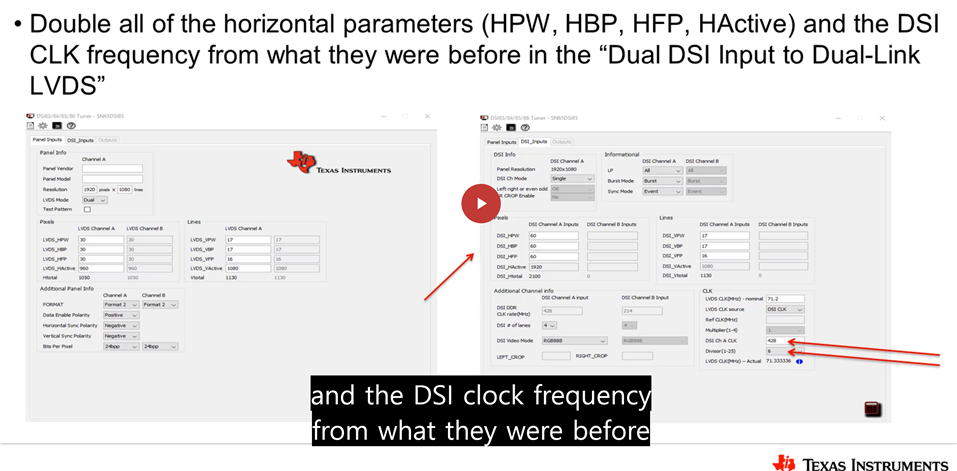

Q2) If it is supported, how can I set it up to output normally? (Currently, the SN65DSI84TPAPRQ1 IC setting was done using the software tool provided by TI.)

Please check. Thank you.