Tool/software:

Hi Team

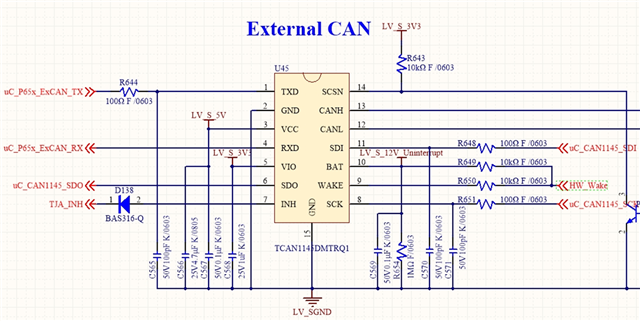

Customer is using TCAN1145 in their OBC product.

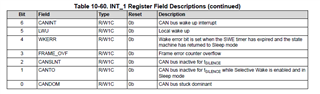

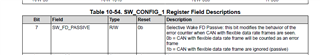

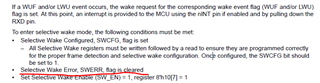

There is an issue in their system: Any frame sent by the host may accidentally wake up the auxiliary source. they configured fixed frame to wake - up, and non - fixed frames will not trigger wake - up.

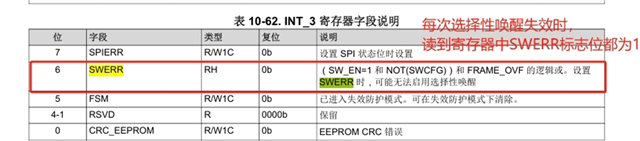

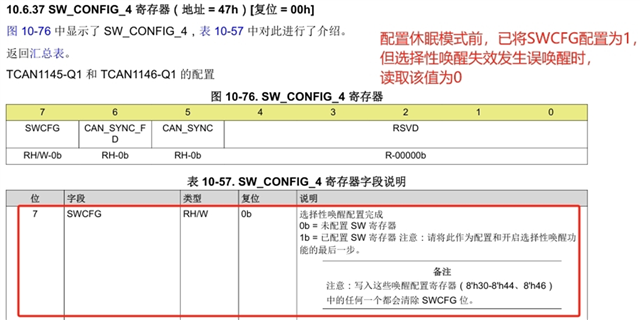

Configured SWCFG=1, it will change to 0 when accidentally wake up.

The following is schematic:

And the customer has ruled out the following: Wake - up via the WAKE pin; the power supply voltage of BAT12V fluctuates between 12.9V - 12.12V, which is within the normal range; both SPI communication, reading and writing are normal.

Their question is :what kind of situation that SWERR will be read as 1( normal prototype is 0)? how to address this issue?