Tool/software:

Hi,

we have a product that uses sn65dsi84 as a bridge from a Linux CPU module that outputs MIPI-DSI to a dual-channel LVDS panel.

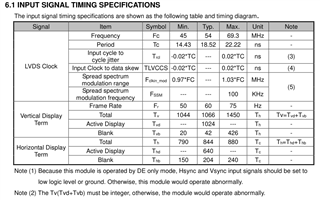

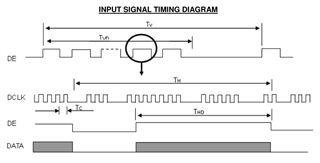

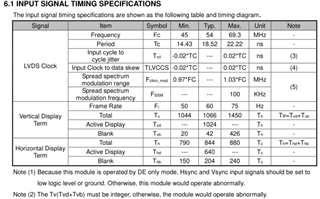

The panel datasheet states the following:

"Because this module is operated by DE only mode, Hsync and Vsync input signals should be set to low logic level or ground. Otherwise, this module would operate abnormally"

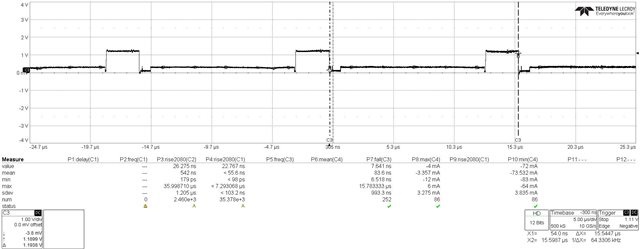

Indeed, in order to make the panel to display our boot logo we had to modify the Linux driver and hard-code Hysnc/Vsync pulse width registers to 0. In this way, we can "simulate" the fact that they must not be used; without this little trick, the screen would simply go blank.

I would like to understand if our "solution" is the intended one for such situations, or if there is a better/correct way to achieve this? I'm asking in particular because we see bit 0xE5.7 being set to 1, which as far as I understand can be ignored in our case as we don't rely on HS/VS.

Thank you in advance!