Tool/software:

Hi Team,

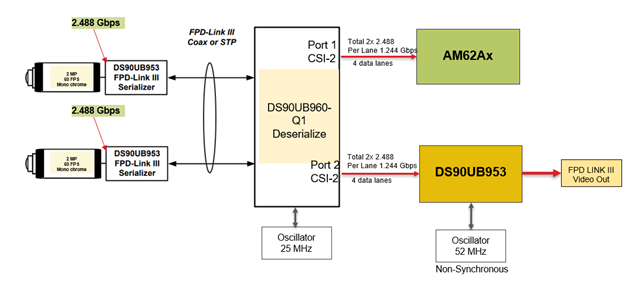

I have some queries regarding this architecture:

Q1. We are using different crystals/oscillators for this architecture individually. Is this acceptable, or do we need to synchronize the same clock for this application concerning the DS90UB953( Non-synchronous).

Q2. Is the structure for video output appropriate?

Q3. Can we compress the Port 2 CSI-2 upto 832 Mbps per lane for DS90UB953 compatibility

Q4.How do both camera data streams come on MIPI CSI-2 in term of packet or media