Part Number: TCAN4550-Q1

Tool/software:

Hello, my issue is identical to this locked thread: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1353491/tcan4550-q1-problems-writing-to-control-register?tisearch=e2e-sitesearch

I have verified that I can read and write using the scratchpad register and the endian test register. The TCAN4x5x_Device_SetMode() function also seems to work correctly

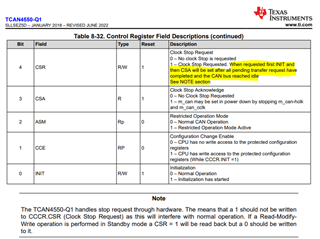

I am using the TCAN4x5x_MCAN_EnableProtectedRegisters() function from the DEMO drivers. The initial read is 0x19. Then it tires to write 0x03 (CCCR_INIT and CCCR_CCE only). The function fails every time and the CCCR register is 0x19 every time it is read. I have added various delays before this function and have set the retries as high as 200 with the same results.

In the above thread, Eric Schott said "It is possible an attempt to unlock the protected registers to fail the MCAN is busy during the request". Can someone elaborate?

Thanks,

-Mike