Tool/software:

HI BU team

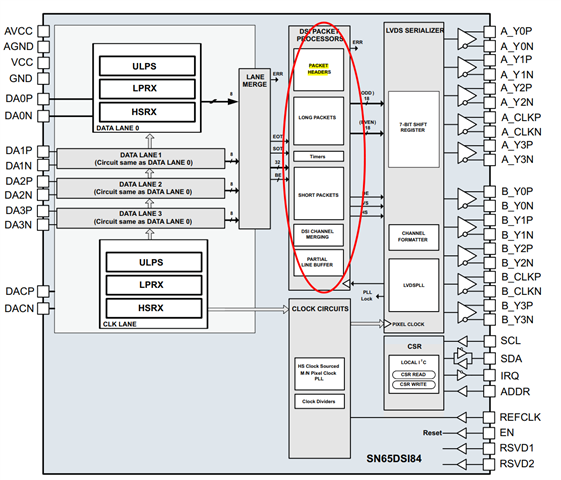

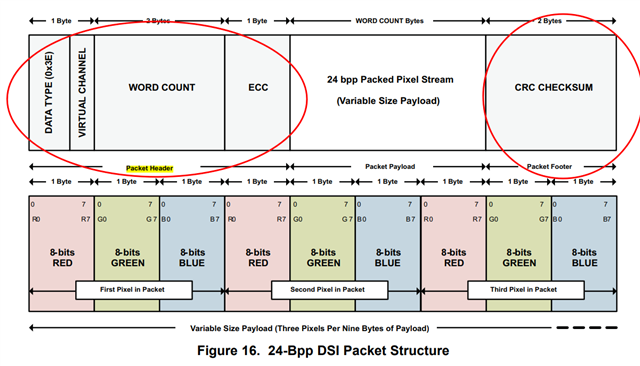

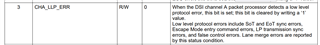

My customer Geely/Ecarx followed the initialization sequence shard in the datasheet and CSR configuration are right but the system always report CHA_CRC_ERR in 0xE5[6] bit when SOC from MTK wake-up from the STR mode and need to re-config DSI84. While no any DSI error is reported when the system is powered-up in the firs time.

So customer wanted to know how SN65DSI84-Q1 detect the CRC error in DSI data lanes. And would you help share the potential causes to help customer to investigate the next step at SOC side?

Thanks