Tool/software:

Dear TI Team,

I have designed a custom board using the DS90UB954TRGZRQ1 deserializer and DS90UB953TRHBRQ1 serializer. We are troubleshooting an issue where the I2C back channel communication is not working.

1. Setup & Configuration:

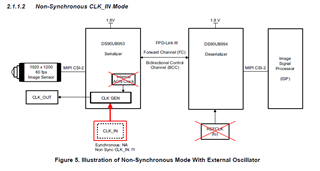

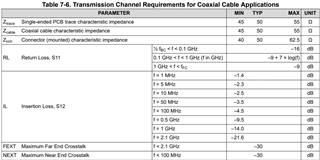

- Deserializer (DS90UB954) and Serializer (DS90UB953) connected via coax cable

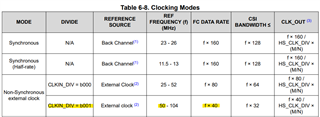

- Non-synchronous mode configuration

- 50MHz external clock provided to serializer

- Deserializer has no external clock

Hardware Configuration:

Deserializer (DS90UB954)

- Mode Config: Pulled down (10KΩ)

- IDX Pin: Pulled down (10KΩ)

- PDB (Power Down) Config: Pulled up (10KΩ) with a 10µF bypass capacitor

- i2c pull up 2.2k

Serializer (DS90UB953)

- Mode Config: 75KΩ pull-up, 35.7KΩ pull-down

- IDX Pin: 40.2KΩ pull-down

- PDB Config: 10KΩ pull-up with 10µF bypass capacitor

- I2C Pull-ups: 2.2KΩ

2. Observations & Steps Taken:

- Powered on the setup, but observed no LOCK established on the deserializer.

- Manually configured serializer register:

After this, the deserializer LOCKED.

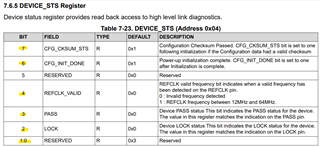

i2cset -y 3 0x18 0x05 0x13 b - Read deserializer register 0x04: Received 0xCF

- Configured deserializer I2C registers:

i2cset -y 3 0x30 0x4c 0x1 bi2cset -y -f 3 0x30 0x6d 0x7c bi2cset -y 3 0x30 0x58 0x7a bi2cset -y 3 0x30 0x5c 0x31 b - Tried to read back a register on the serializer:

No response received.

3. Issues Faced:

- Deserializer does not lock initially until I manually write to the serializer register.

- Unable to read serializer registers over the back channel.

- Status register 0x04 on deserializer reads 0xCF

4. Questions:

- Is there a necessary initialization sequence for proper link and I2C back channel communication?

- Why is the deserializer not locking initially until I manually configure the serializer?

- Is my I2C configuration sequence correct?

- Any recommended debug steps to check back channel I2C functionality?

Any guidance would be highly appreciated.

Thank you!