Part Number: PCA9545A

Tool/software:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

The eight data bits and the ACK/NACK bit are sampled at the rising edge of SCL.

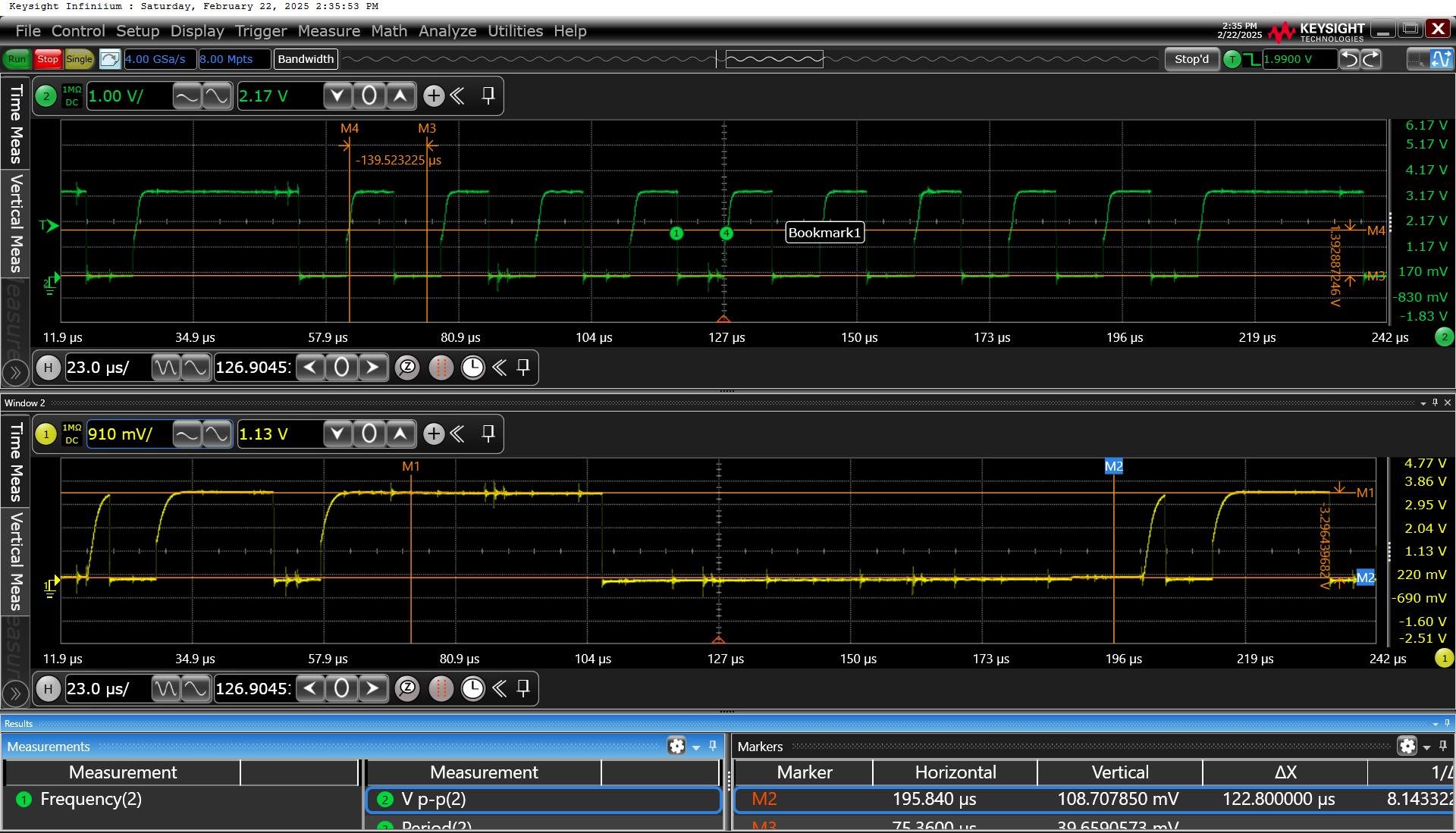

In this example, the ACK bit is sampled at 196 µs. The ACK bit was driven low by the slave, while the following low level is driven by the master in order to send the stop condition. While the switch-over between slave and master happens, the SDA line might go high for a short time; this is normal and not a problem.