Tool/software:

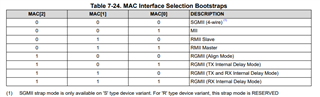

May I know if I use 100baseT1,what need to be config for RGMII? I currently set RGMII enabled and align mode and during strap setting since SOC MAC mode can not set delay time.

I look into the datasheet there is no example and no local FAE can support this topic.

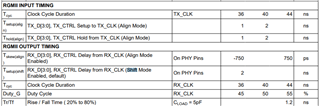

- if I set RGMII align mode what is delay status of power up after strap take effect?

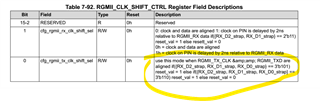

- what is the differences between RGMII (TX and RX Internal Delay Mode) and RGMII (Align Mode)?

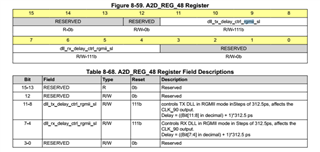

- if I set dll_tx_delay_ctrl_rgmii_sl =5ns by MDIO way, is there any problem?

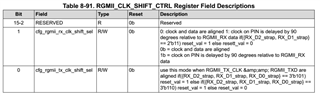

- Do I need to set cfg_rgmii_tx_clk_shift_sel? if clock is delay 90 degree, Sicne the clock is 40ns, clk is delay 10ns. Do I need to set addtional delay by dll_tx_delay_ctrl_rgmii_sl=5ns? if yes then total delay would be 15ns?