Other Parts Discussed in Thread: LMK04832,

Tool/software:

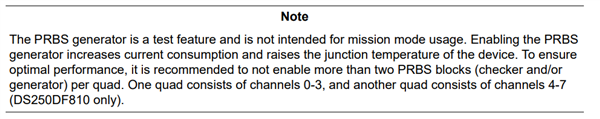

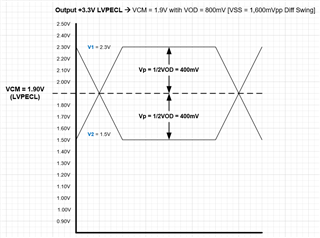

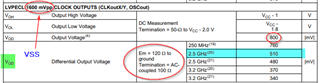

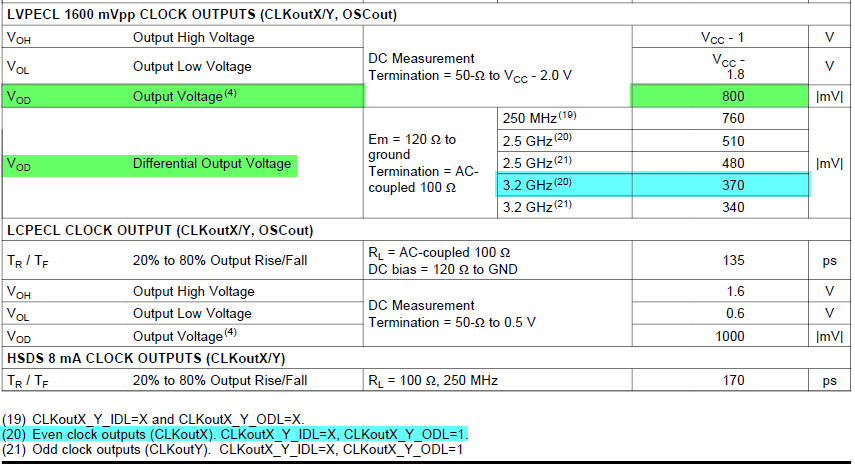

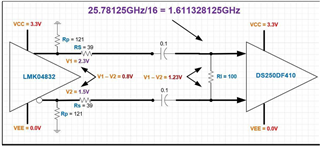

I am interested in using the DS250DF410 for PRBS testing at 25.78125GHz in a 3U VPX Backplane. My plan is to design a 3U VPX Plug-In Card that will contain a DS250DF410 Re-Timer. Four of the Tx Ports {x4} and Four of the Rx Ports {x4} will be routed to the 3U VPX Connector [Data Plane]. In the Backplane, the Data Plane from the 3U VPX Re-Timer Plug-In Card is routed to a 3U VPX Switch Card. When using the DS250DF410 to "Generate" PRBS Data @ 25.78125GHz, I plan to use an LMK04832 [Also located on the DS250DF410 3U VPX Plug-In Card] to generate (4) Copies of a Sub-Rate Clock of 25.78125GHz/16 = 1.611328125GHz. Each Copy of the 1.611328125GHz Clock from the Output of the LMK04832 will be AC-Coupled to Each of the Rx Ports on the DS250DF410. The (4) Output Clocks from the LMK04832 @ 1.611328125GHz will be configured as LVPECL 1600mVpp. From the Data Sheet of the LMK04832 shown below, the Expected Vod @ 3.2GHz is 370mVpp when Each Output Leg is Terminated to Ground with a 120Ohm Resistor, and then AC-Coupled to a 100Ohm Load.

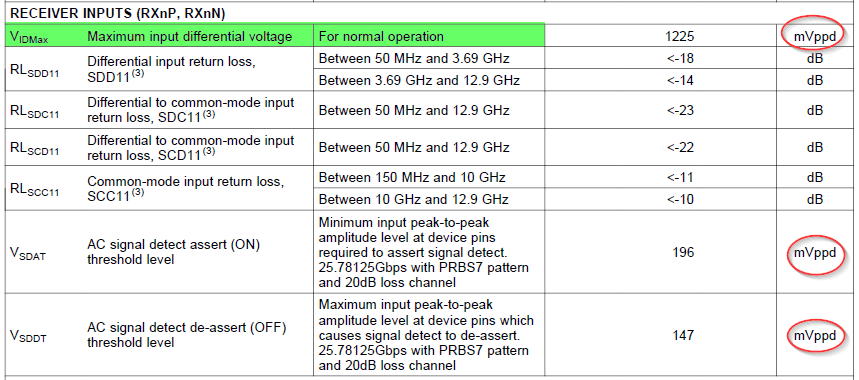

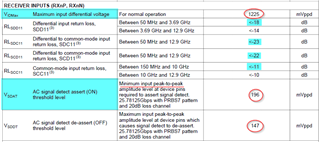

From the Data Sheet of the DS250DF410 shown below, Maximum Vid = 1225mVpp and Vdsat = 196mVpp [With Signal Detect Assert = "On"]

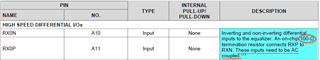

Input Termination to Each DS250DF410 Rx Port is 100Ohms [See Below]:

LMK04832 to DS250DF410 Circuit Shown Below:

LMK Output is 800mVpp when DC-Coupled and 370mVpp with Each Leg Terminated to 120Ohm and AC-Coupled to a 100Ohm Load [DS250DF410].

Will the Design Concept Described/Shown work properly to Generate PRBS Data @ 25.78125GHz at the (4) Tx Ports of the DS250DF410?